2Packaging Technology

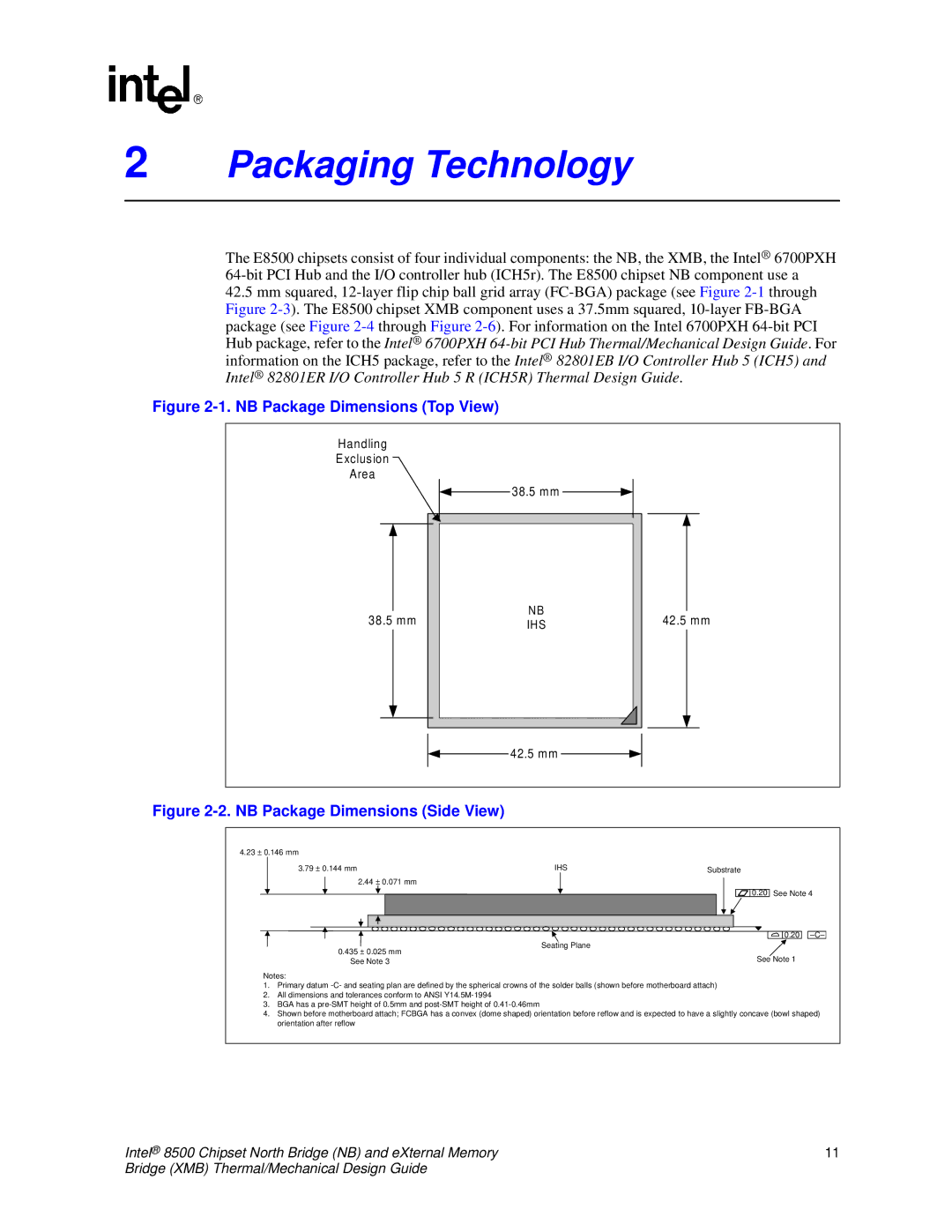

The E8500 chipsets consist of four individual components: the NB, the XMB, the Intel® 6700PXH

42.5mm squared,

Figure 2-1. NB Package Dimensions (Top View)

Handling |

|

| |

Exclusion |

|

| |

Area |

|

| |

| 38.5 mm |

| |

| NB |

| |

38.5 mm | TNB | 42.5 mm | |

IHIHS | |||

|

| ||

| 42.5 mm |

|

Figure 2-2. NB Package Dimensions (Side View)

4.23 ± 0.146 mm

3.79 ± 0.144 mm | IHS | Substrate |

2.44 ± 0.071 mm

![]()

![]()

![]() 0.20 See Note 4

0.20 See Note 4

![]()

![]()

![]() 0.20

0.20 ![]()

![]()

0.435 ± 0.025 mm | Seating Plane | |

See Note 1 | ||

See Note 3 |

Notes:

1.Primary datum

2.All dimensions and tolerances conform to ANSI

3.BGA has a

4.Shown before motherboard attach; FCBGA has a convex (dome shaped) orientation before reflow and is expected to have a slightly concave (bowl shaped) orientation after reflow

Intel® 8500 Chipset North Bridge (NB) and eXternal Memory | 11 |

Bridge (XMB) Thermal/Mechanical Design Guide |

|