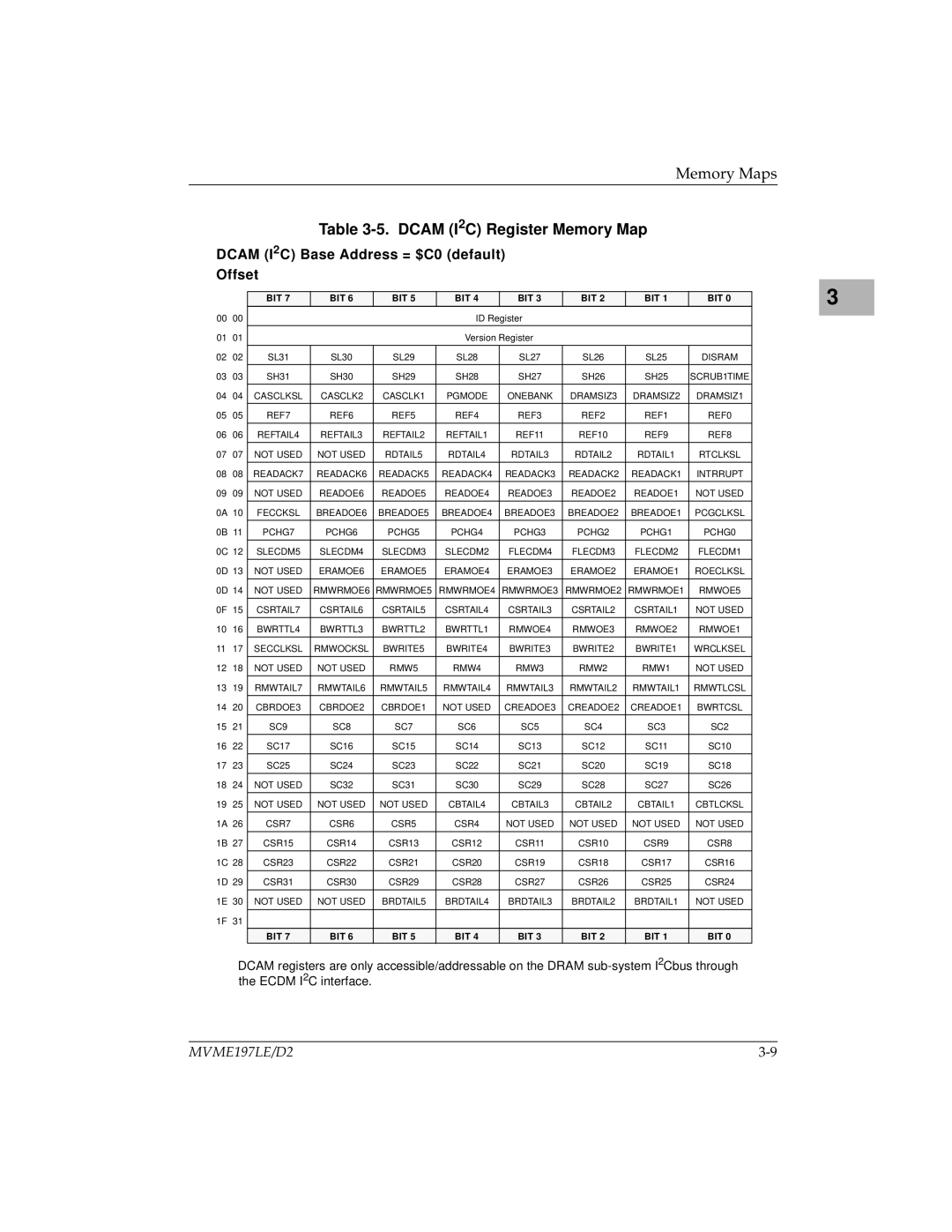

Memory Maps

Table 3-5. DCAM (I2C) Register Memory Map

DCAM (I2C) Base Address = $C0 (default)

Offset

|

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

00 | 00 |

|

|

| ID Register |

|

|

| |

01 | 01 |

|

|

| Version Register |

|

|

| |

02 | 02 | SL31 | SL30 | SL29 | SL28 | SL27 | SL26 | SL25 | DISRAM |

|

|

|

|

|

|

|

|

|

|

03 | 03 | SH31 | SH30 | SH29 | SH28 | SH27 | SH26 | SH25 | SCRUB1TIME |

|

|

|

|

|

|

|

|

|

|

04 | 04 | CASCLKSL | CASCLK2 | CASCLK1 | PGMODE | ONEBANK | DRAMSIZ3 | DRAMSIZ2 | DRAMSIZ1 |

05 | 05 | REF7 | REF6 | REF5 | REF4 | REF3 | REF2 | REF1 | REF0 |

|

|

|

|

|

|

|

|

|

|

06 | 06 | REFTAIL4 | REFTAIL3 | REFTAIL2 | REFTAIL1 | REF11 | REF10 | REF9 | REF8 |

|

|

|

|

|

|

|

|

|

|

07 | 07 | NOT USED | NOT USED | RDTAIL5 | RDTAIL4 | RDTAIL3 | RDTAIL2 | RDTAIL1 | RTCLKSL |

|

|

|

|

|

|

|

|

|

|

08 | 08 | READACK7 | READACK6 | READACK5 | READACK4 | READACK3 | READACK2 | READACK1 | INTRRUPT |

|

|

|

|

|

|

|

|

|

|

09 | 09 | NOT USED | READOE6 | READOE5 | READOE4 | READOE3 | READOE2 | READOE1 | NOT USED |

|

|

|

|

|

|

|

|

| |

0A 10 | FECCKSL | BREADOE6 | BREADOE5 | BREADOE4 | BREADOE3 | BREADOE2 | BREADOE1 | PCGCLKSL | |

0B 11 | PCHG7 | PCHG6 | PCHG5 | PCHG4 | PCHG3 | PCHG2 | PCHG1 | PCHG0 | |

|

|

|

|

|

|

|

|

| |

0C 12 | SLECDM5 | SLECDM4 | SLECDM3 | SLECDM2 | FLECDM4 | FLECDM3 | FLECDM2 | FLECDM1 | |

|

|

|

|

|

|

|

|

| |

0D 13 | NOT USED | ERAMOE6 | ERAMOE5 | ERAMOE4 | ERAMOE3 | ERAMOE2 | ERAMOE1 | ROECLKSL | |

|

|

|

|

|

|

|

|

| |

0D 14 | NOT USED | RMWRMOE6 | RMWRMOE5 | RMWRMOE4 | RMWRMOE3 | RMWRMOE2 | RMWRMOE1 | RMWOE5 | |

|

|

|

|

|

|

|

|

| |

0F 15 | CSRTAIL7 | CSRTAIL6 | CSRTAIL5 | CSRTAIL4 | CSRTAIL3 | CSRTAIL2 | CSRTAIL1 | NOT USED | |

|

|

|

|

|

|

|

|

|

|

10 | 16 | BWRTTL4 | BWRTTL3 | BWRTTL2 | BWRTTL1 | RMWOE4 | RMWOE3 | RMWOE2 | RMWOE1 |

11 | 17 | SECCLKSL | RMWOCKSL | BWRITE5 | BWRITE4 | BWRITE3 | BWRITE2 | BWRITE1 | WRCLKSEL |

|

|

|

|

|

|

|

|

|

|

12 | 18 | NOT USED | NOT USED | RMW5 | RMW4 | RMW3 | RMW2 | RMW1 | NOT USED |

|

|

|

|

|

|

|

|

|

|

13 | 19 | RMWTAIL7 | RMWTAIL6 | RMWTAIL5 | RMWTAIL4 | RMWTAIL3 | RMWTAIL2 | RMWTAIL1 | RMWTLCSL |

|

|

|

|

|

|

|

|

|

|

14 | 20 | CBRDOE3 | CBRDOE2 | CBRDOE1 | NOT USED | CREADOE3 | CREADOE2 | CREADOE1 | BWRTCSL |

|

|

|

|

|

|

|

|

|

|

15 | 21 | SC9 | SC8 | SC7 | SC6 | SC5 | SC4 | SC3 | SC2 |

|

|

|

|

|

|

|

|

|

|

16 | 22 | SC17 | SC16 | SC15 | SC14 | SC13 | SC12 | SC11 | SC10 |

17 | 23 | SC25 | SC24 | SC23 | SC22 | SC21 | SC20 | SC19 | SC18 |

|

|

|

|

|

|

|

|

|

|

18 | 24 | NOT USED | SC32 | SC31 | SC30 | SC29 | SC28 | SC27 | SC26 |

|

|

|

|

|

|

|

|

|

|

19 | 25 | NOT USED | NOT USED | NOT USED | CBTAIL4 | CBTAIL3 | CBTAIL2 | CBTAIL1 | CBTLCKSL |

1A 26 | CSR7 | CSR6 | CSR5 | CSR4 | NOT USED | NOT USED | NOT USED | NOT USED | |

|

|

|

|

|

|

|

|

| |

1B 27 | CSR15 | CSR14 | CSR13 | CSR12 | CSR11 | CSR10 | CSR9 | CSR8 | |

|

|

|

|

|

|

|

|

| |

1C 28 | CSR23 | CSR22 | CSR21 | CSR20 | CSR19 | CSR18 | CSR17 | CSR16 | |

|

|

|

|

|

|

|

|

| |

1D 29 | CSR31 | CSR30 | CSR29 | CSR28 | CSR27 | CSR26 | CSR25 | CSR24 | |

|

|

|

|

|

|

|

|

| |

1E 30 | NOT USED | NOT USED | BRDTAIL5 | BRDTAIL4 | BRDTAIL3 | BRDTAIL2 | BRDTAIL1 | NOT USED | |

1F | 31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

DCAM registers are only accessible/addressable on the DRAM

3 |

MVME197LE/D2 |