Chapter 7: Designing with the SX-550

OEM Header Interface

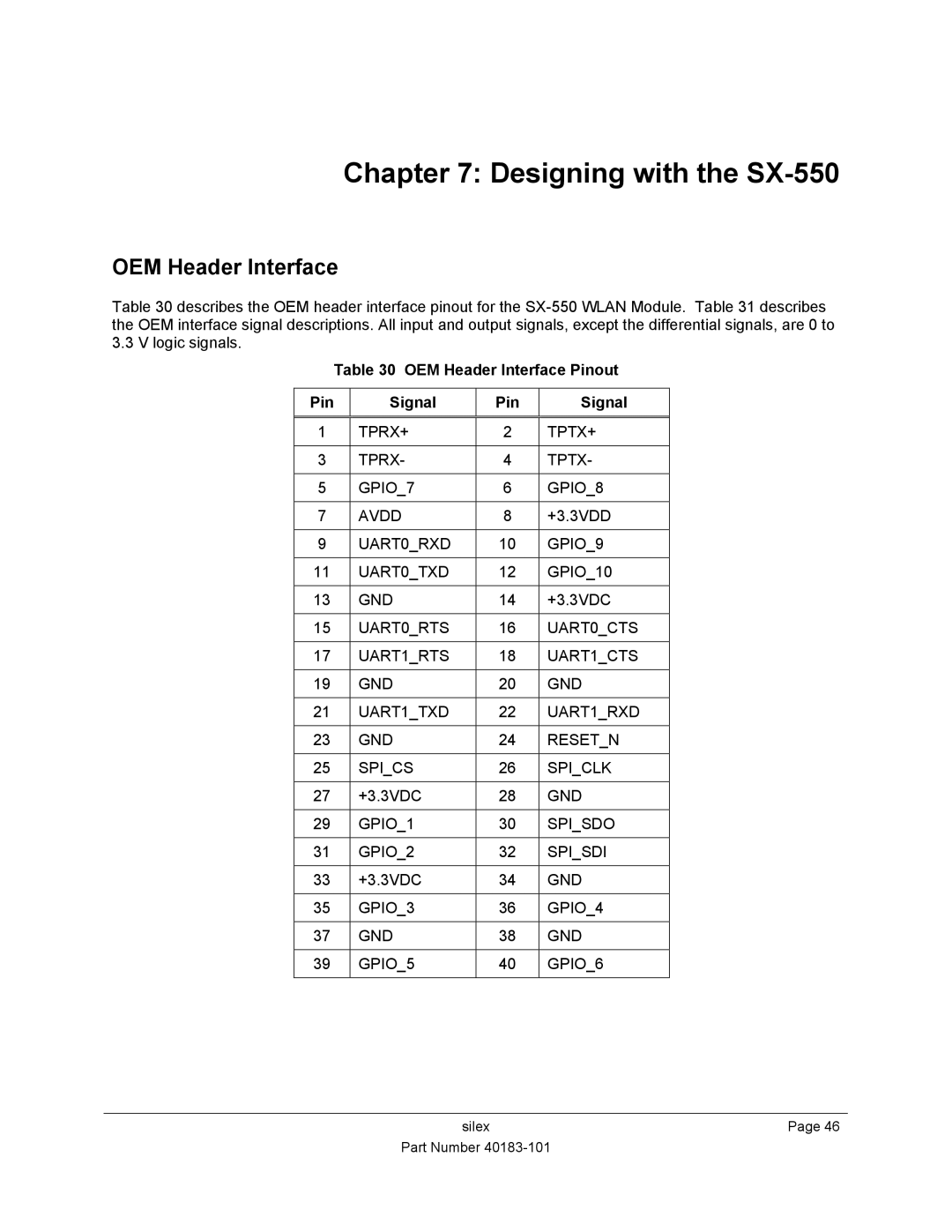

Table 30 describes the OEM header interface pinout for the

Table 30 OEM Header Interface Pinout

Pin | Signal | Pin | Signal |

|

|

|

|

1 | TPRX+ | 2 | TPTX+ |

|

|

|

|

3 | TPRX- | 4 | TPTX- |

|

|

|

|

5 | GPIO_7 | 6 | GPIO_8 |

|

|

|

|

7 | AVDD | 8 | +3.3VDD |

|

|

|

|

9 | UART0_RXD | 10 | GPIO_9 |

|

|

|

|

11 | UART0_TXD | 12 | GPIO_10 |

|

|

|

|

13 | GND | 14 | +3.3VDC |

|

|

|

|

15 | UART0_RTS | 16 | UART0_CTS |

|

|

|

|

17 | UART1_RTS | 18 | UART1_CTS |

|

|

|

|

19 | GND | 20 | GND |

|

|

|

|

21 | UART1_TXD | 22 | UART1_RXD |

|

|

|

|

23 | GND | 24 | RESET_N |

|

|

|

|

25 | SPI_CS | 26 | SPI_CLK |

|

|

|

|

27 | +3.3VDC | 28 | GND |

|

|

|

|

29 | GPIO_1 | 30 | SPI_SDO |

|

|

|

|

31 | GPIO_2 | 32 | SPI_SDI |

|

|

|

|

33 | +3.3VDC | 34 | GND |

|

|

|

|

35 | GPIO_3 | 36 | GPIO_4 |

|

|

|

|

37 | GND | 38 | GND |

|

|

|

|

39 | GPIO_5 | 40 | GPIO_6 |

|

|

|

|

silex | Page 46 |

Part Number |

|