FIFO Mode | Overview |

|

|

FIFO Mode

Overview

General Information

The FIFO mode allows to record data continuously and trans- fer it online to the PC (acquisition boards) or allows to write data continuously from the PC to the board (generation boards). Therefore the

FIFO mode uses interrupts and is supported by the drivers on 32 bit operating systems like Window 9x/ME, Windows NT/2000/XP or Linux. Start of FIFO mode waits for a trigger event. If you wish to start FIFO mode immediately, you may use the software trigger.FIFO mode can be used together with the options Multiple Recording/Replay and Gated Sampling/Replay. Details on this can be found in the appropriate chapters about the options.

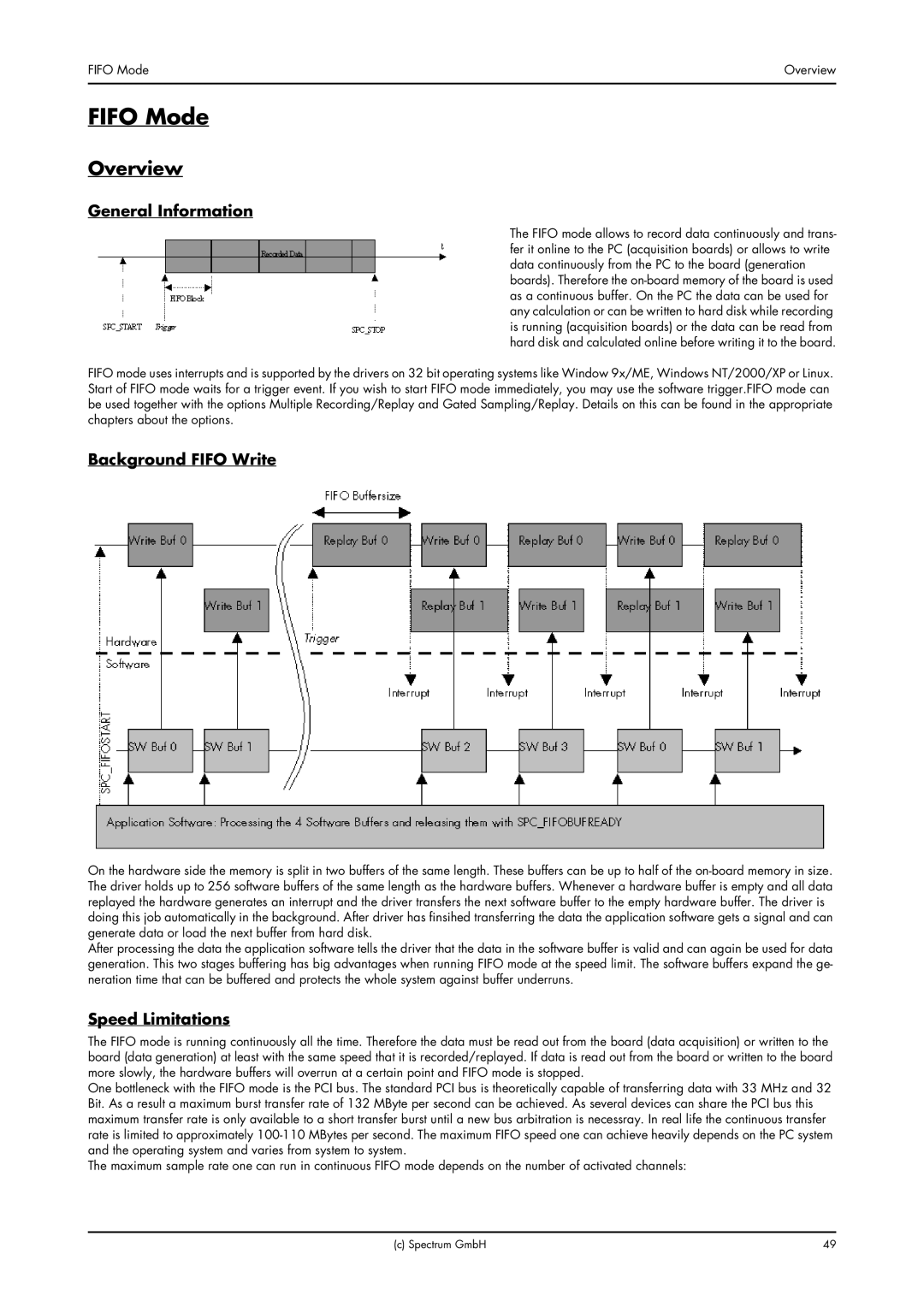

Background FIFO Write

On the hardware side the memory is split in two buffers of the same length. These buffers can be up to half of the

After processing the data the application software tells the driver that the data in the software buffer is valid and can again be used for data generation. This two stages buffering has big advantages when running FIFO mode at the speed limit. The software buffers expand the ge- neration time that can be buffered and protects the whole system against buffer underruns.

Speed Limitations

The FIFO mode is running continuously all the time. Therefore the data must be read out from the board (data acquisition) or written to the board (data generation) at least with the same speed that it is recorded/replayed. If data is read out from the board or written to the board more slowly, the hardware buffers will overrun at a certain point and FIFO mode is stopped.

One bottleneck with the FIFO mode is the PCI bus. The standard PCI bus is theoretically capable of transferring data with 33 MHz and 32 Bit. As a result a maximum burst transfer rate of 132 MByte per second can be achieved. As several devices can share the PCI bus this maximum transfer rate is only available to a short transfer burst until a new bus arbitration is necessray. In real life the continuous transfer rate is limited to approximately

The maximum sample rate one can run in continuous FIFO mode depends on the number of activated channels:

(c) Spectrum GmbH | 49 |