Programming | FIFO Mode |

|

|

FIFO mode

In normal applications the FIFO mode will run in a loop and process one buffer after the other. There are a few special commands and regi- sters for the FIFO mode:

Register | Value | Direction | Description | |

SPC_COMMAND | 0 | w | Command register. Allowed values for FIFO mode are listed below | |

| SPC_FIFOSTART | 12 | Starts the FIFO mode and waits for the first interrupt | |

|

|

|

| |

| SPC_FIFOWAIT | 13 | Waits for the next buffer interrupt | |

|

|

|

| |

| SPC_STOP | 20 | Stops the FIFO mode | |

The start command and the wait command both wait for the signal from the driver that the next buffer has to be processed. This signal is generated by the driver on receiving an interrupt from the hardware. While waiting none of these commands waiste cpu power (no polling mode). If for any reason the signal is not coming from the hardware (e.g. trigger is not found) the FIFO mode must be stopped from a second task with a stop command.

This handshake command tells the driver that the application has finished it’s work with the software buffer. The both commands

SPC_FIFOWAIT (SPC_FIFOSTART) and SPC_FIFO_BUFFERS form a simple but powerful handshake protocol between application software and board driver.

Register | Value | Direction | Description |

SPC_FIFO_BUFREADY | 60050 | w | FIFO mode handshake. Application has finsihed with that buffer. Value is index of buffer |

Backward compatibility: This register replaces the formerly known SPC_FIFO_BUFREADY0 ...

SPC_FIFO_BUFREADY15 commands. It has the same functionality but can handle more FIFO buffers. For back- ward compatibility the older commands still work but are still limited to 16 buffers.

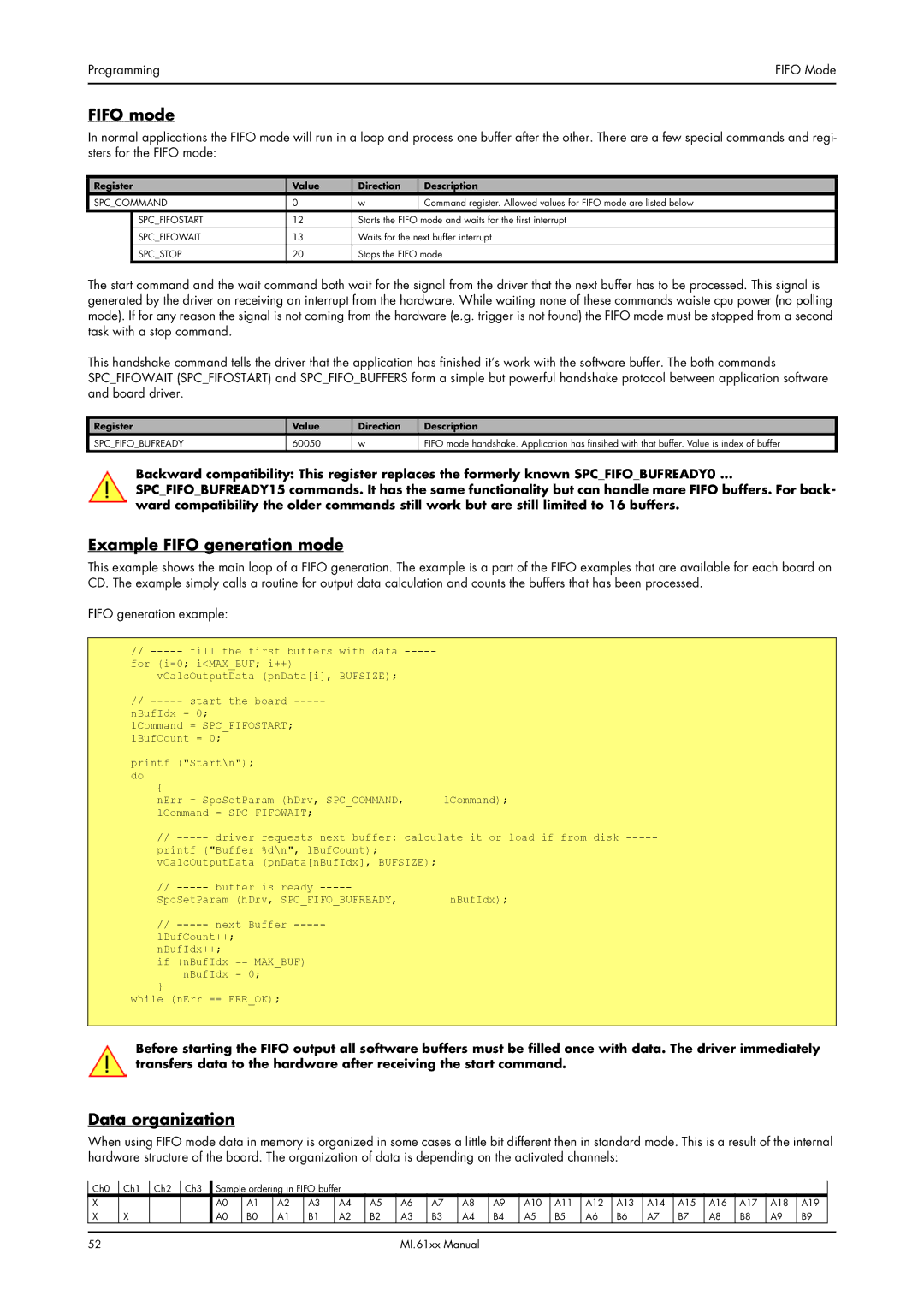

Example FIFO generation mode

This example shows the main loop of a FIFO generation. The example is a part of the FIFO examples that are available for each board on CD. The example simply calls a routine for output data calculation and counts the buffers that has been processed.

FIFO generation example:

//

for (i=0; i<MAX_BUF; i++) vCalcOutputData (pnData[i], BUFSIZE);

//

nBufIdx = 0;

lCommand = SPC_FIFOSTART; lBufCount = 0;

printf ("Start\n"); do

{

nErr = SpcSetParam (hDrv, SPC_COMMAND, lCommand); lCommand = SPC_FIFOWAIT;

//

printf ("Buffer %d\n", lBufCount); vCalcOutputData (pnData[nBufIdx], BUFSIZE);

//

SpcSetParam | (hDrv, SPC_FIFO_BUFREADY, | nBufIdx); |

// |

| |

lBufCount++; |

|

|

nBufIdx++; | == MAX_BUF) |

|

if (nBufIdx |

| |

nBufIdx | = 0; |

|

} |

|

|

while (nErr == ERR_OK);

Before starting the FIFO output all software buffers must be filled once with data. The driver immediately transfers data to the hardware after receiving the start command.

Data organization

When using FIFO mode data in memory is organized in some cases a little bit different then in standard mode. This is a result of the internal hardware structure of the board. The organization of data is depending on the activated channels:

Ch0 | Ch1 | Ch2 | Ch3 | Sample ordering in FIFO buffer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

X |

|

|

| A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 |

|

X | X |

|

| A0 | B0 | A1 | B1 | A2 | B2 | A3 | B3 | A4 | B4 | A5 | B5 | A6 | B6 | A7 | B7 | A8 | B8 | A9 | B9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 | MI.61xx Manual |