Programming | FIFO Mode |

|

|

|

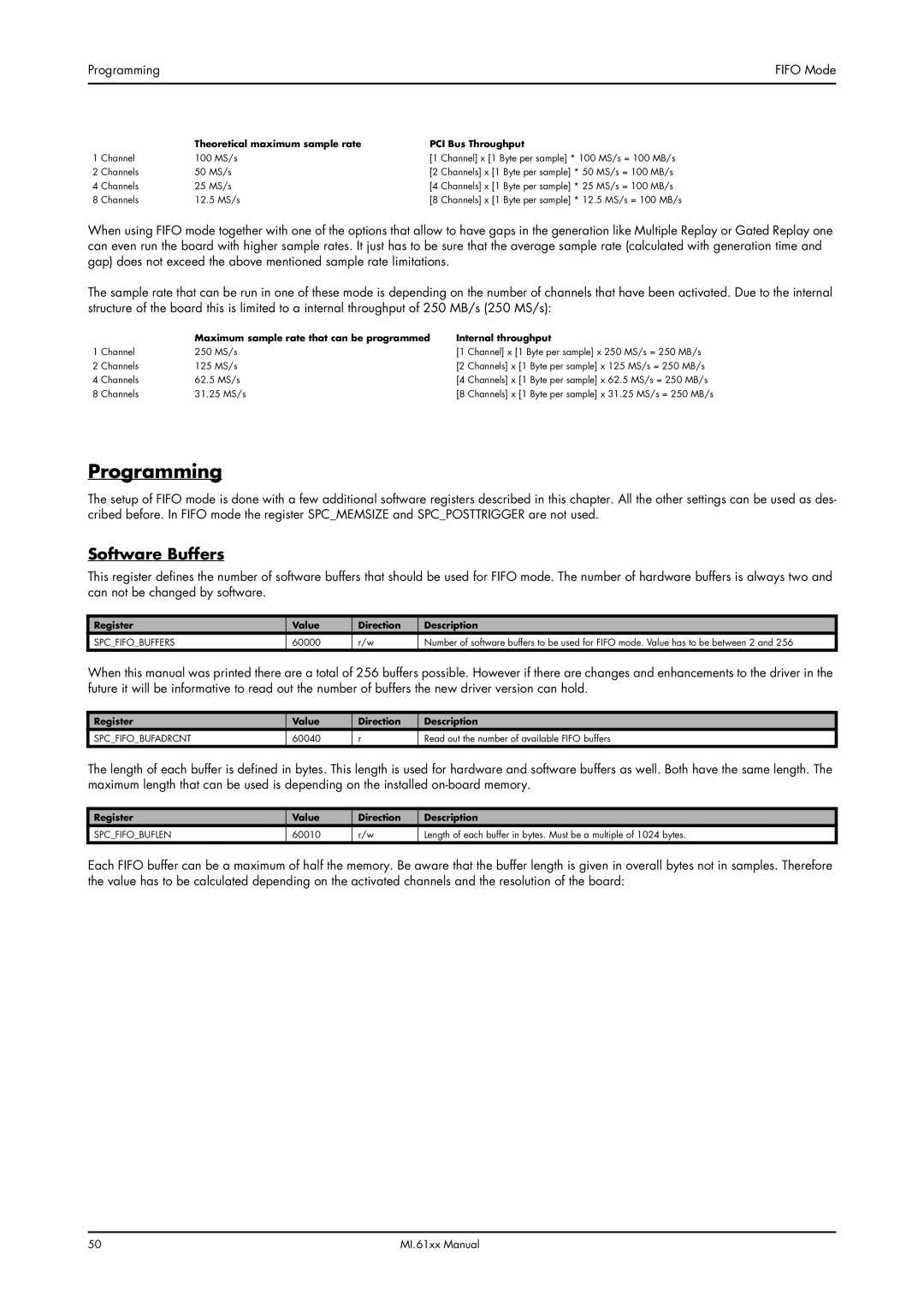

| Theoretical maximum sample rate | PCI Bus Throughput |

1 | Channel | 100 MS/s | [1 Channel] x [1 Byte per sample] * 100 MS/s = 100 MB/s |

2 | Channels | 50 MS/s | [2 Channels] x [1 Byte per sample] * 50 MS/s = 100 MB/s |

4 | Channels | 25 MS/s | [4 Channels] x [1 Byte per sample] * 25 MS/s = 100 MB/s |

8 | Channels | 12.5 MS/s | [8 Channels] x [1 Byte per sample] * 12.5 MS/s = 100 MB/s |

When using FIFO mode together with one of the options that allow to have gaps in the generation like Multiple Replay or Gated Replay one can even run the board with higher sample rates. It just has to be sure that the average sample rate (calculated with generation time and gap) does not exceed the above mentioned sample rate limitations.

The sample rate that can be run in one of these mode is depending on the number of channels that have been activated. Due to the internal structure of the board this is limited to a internal throughput of 250 MB/s (250 MS/s):

|

| Maximum sample rate that can be programmed | Internal throughput |

1 | Channel | 250 MS/s | [1 Channel] x [1 Byte per sample] x 250 MS/s = 250 MB/s |

2 | Channels | 125 MS/s | [2 Channels] x [1 Byte per sample] x 125 MS/s = 250 MB/s |

4 | Channels | 62.5 MS/s | [4 Channels] x [1 Byte per sample] x 62.5 MS/s = 250 MB/s |

8 | Channels | 31.25 MS/s | [8 Channels] x [1 Byte per sample] x 31.25 MS/s = 250 MB/s |

Programming

The setup of FIFO mode is done with a few additional software registers described in this chapter. All the other settings can be used as des- cribed before. In FIFO mode the register SPC_MEMSIZE and SPC_POSTTRIGGER are not used.

Software Buffers

This register defines the number of software buffers that should be used for FIFO mode. The number of hardware buffers is always two and can not be changed by software.

Register | Value | Direction | Description |

SPC_FIFO_BUFFERS | 60000 | r/w | Number of software buffers to be used for FIFO mode. Value has to be between 2 and 256 |

When this manual was printed there are a total of 256 buffers possible. However if there are changes and enhancements to the driver in the future it will be informative to read out the number of buffers the new driver version can hold.

Register | Value | Direction | Description |

SPC_FIFO_BUFADRCNT | 60040 | r | Read out the number of available FIFO buffers |

The length of each buffer is defined in bytes. This length is used for hardware and software buffers as well. Both have the same length. The maximum length that can be used is depending on the installed

Register | Value | Direction | Description |

SPC_FIFO_BUFLEN | 60010 | r/w | Length of each buffer in bytes. Must be a multiple of 1024 bytes. |

Each FIFO buffer can be a maximum of half the memory. Be aware that the buffer length is given in overall bytes not in samples. Therefore the value has to be calculated depending on the activated channels and the resolution of the board:

50 | MI.61xx Manual |