Clock generation |

|

|

|

| Internally generated sample rate | |

|

|

|

|

|

|

|

Example: |

|

|

|

|

|

|

|

|

|

|

| ||

SpcSetParam (hDrv, SPC_CHENABLE, | CHANNEL0 | CHANNEL1 CHANNEL2 CHANNEL3); // | activate | all 4 channels | ||

SpcSetParam (hDrv, SPC_EXTERNALCLOCK, | 1); |

| // | activate | external clock | |

SpcSetParam (hDrv, SPC_EXTERNRANGE, EXRANGE_BURST_M); | // set external range to Burst M | |||||

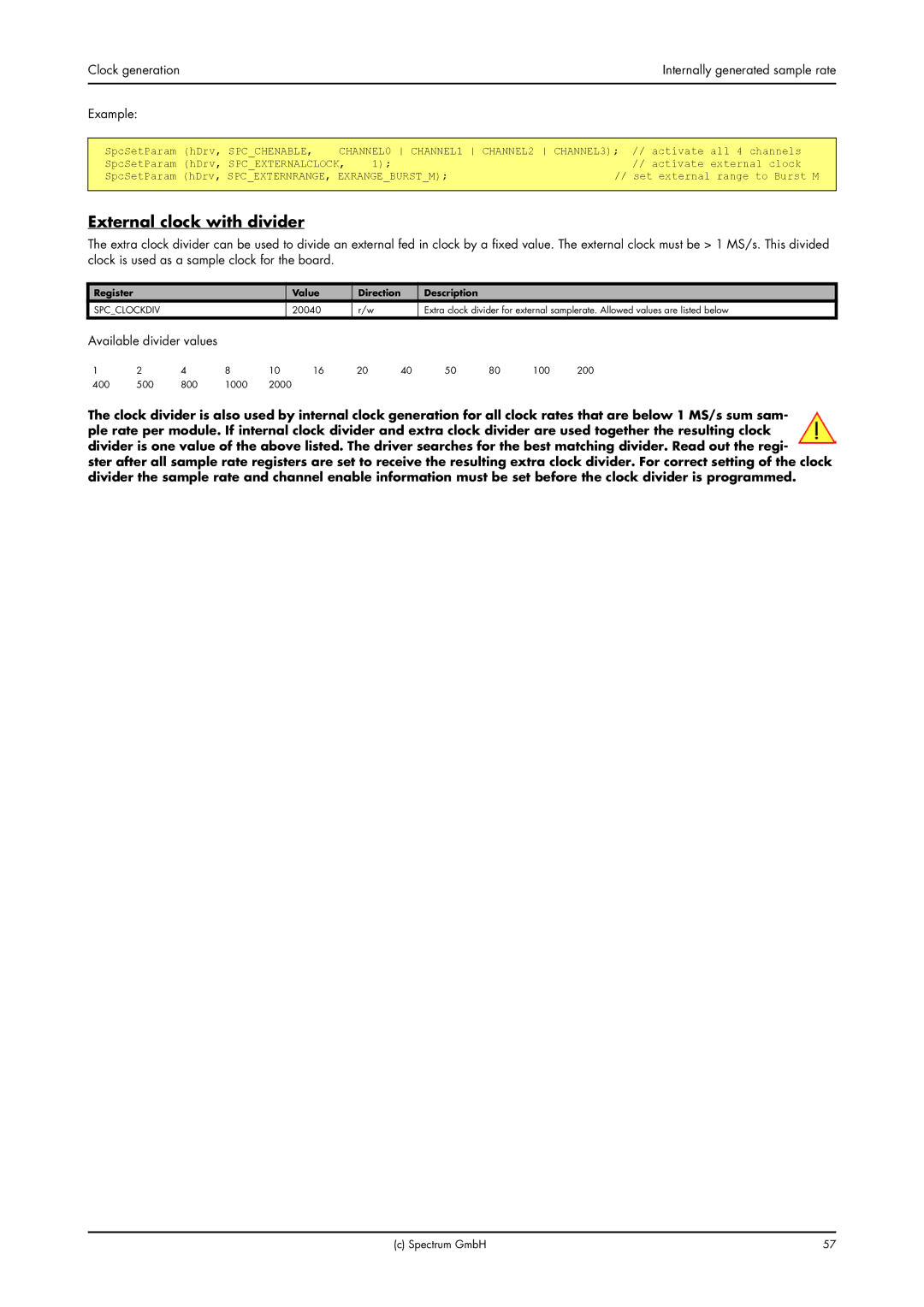

External clock with divider

The extra clock divider can be used to divide an external fed in clock by a fixed value. The external clock must be > 1 MS/s. This divided clock is used as a sample clock for the board.

Register | Value | Direction | Description |

SPC_CLOCKDIV | 20040 | r/w | Extra clock divider for external samplerate. Allowed values are listed below |

Available divider values

1 | 2 | 4 | 8 | 10 | 16 | 20 | 40 | 50 | 80 | 100 | 200 |

400 | 500 | 800 | 1000 | 2000 |

|

|

|

|

|

|

|

The clock divider is also used by internal clock generation for all clock rates that are below 1 MS/s sum sam- ple rate per module. If internal clock divider and extra clock divider are used together the resulting clock divider is one value of the above listed. The driver searches for the best matching divider. Read out the regi-

ster after all sample rate registers are set to receive the resulting extra clock divider. For correct setting of the clock divider the sample rate and channel enable information must be set before the clock divider is programmed.

(c) Spectrum GmbH | 57 |