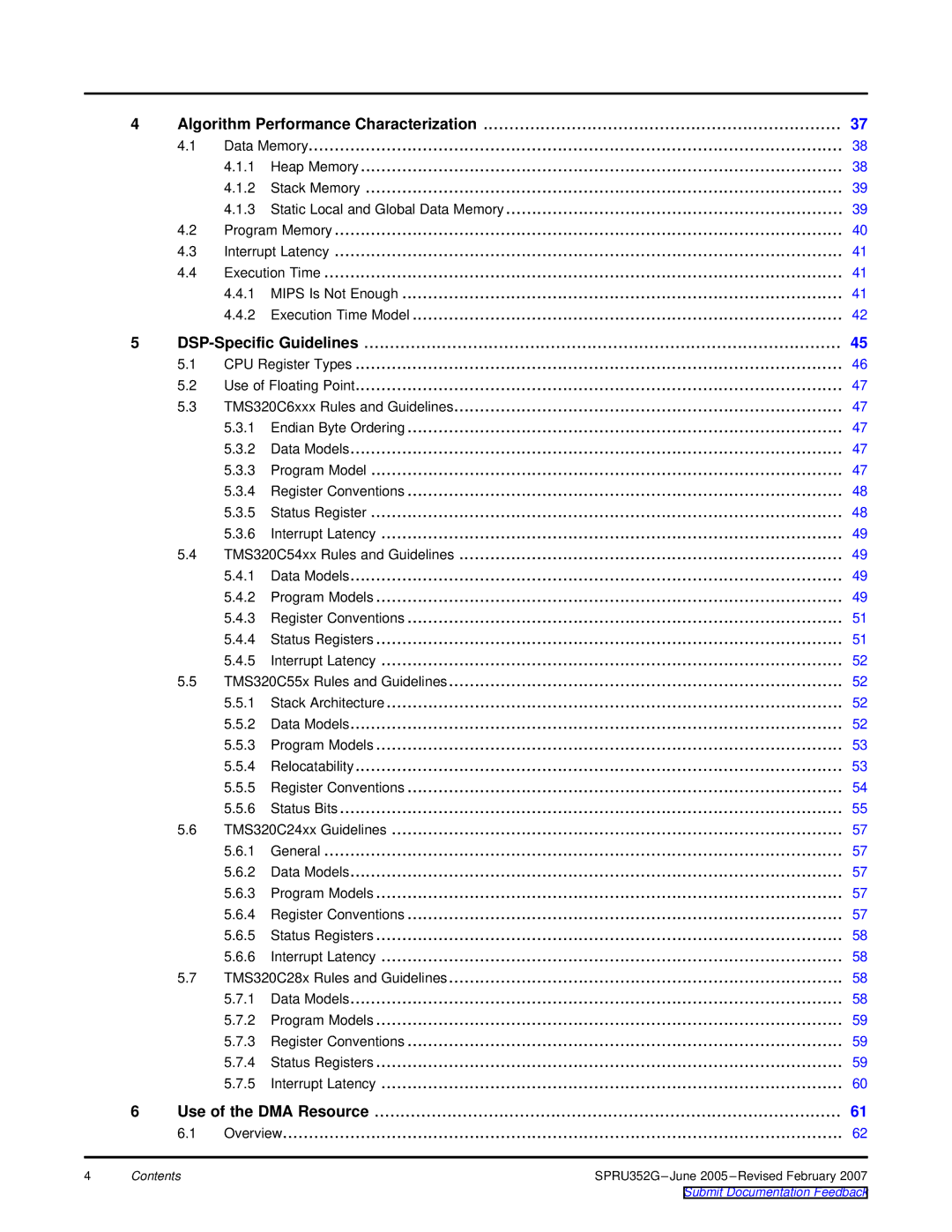

4 | Algorithm Performance Characterization | 37 | ||

| 4.1 | Data Memory | 38 | |

|

| 4.1.1 | Heap Memory | 38 |

|

| 4.1.2 | Stack Memory | 39 |

|

| 4.1.3 Static Local and Global Data Memory | 39 | |

| 4.2 | Program Memory | 40 | |

| 4.3 | Interrupt Latency | 41 | |

| 4.4 | Execution Time | 41 | |

|

| 4.4.1 MIPS Is Not Enough | 41 | |

|

| 4.4.2 | Execution Time Model | 42 |

5 | 45 | |||

| 5.1 | CPU Register Types | 46 | |

| 5.2 | Use of Floating Point | 47 | |

| 5.3 | TMS320C6xxx Rules and Guidelines | 47 | |

|

| 5.3.1 | Endian Byte Ordering | 47 |

|

| 5.3.2 | Data Models | 47 |

|

| 5.3.3 | Program Model | 47 |

|

| 5.3.4 | Register Conventions | 48 |

|

| 5.3.5 | Status Register | 48 |

|

| 5.3.6 | Interrupt Latency | 49 |

| 5.4 | TMS320C54xx Rules and Guidelines | 49 | |

|

| 5.4.1 | Data Models | 49 |

|

| 5.4.2 | Program Models | 49 |

|

| 5.4.3 | Register Conventions | 51 |

|

| 5.4.4 | Status Registers | 51 |

|

| 5.4.5 | Interrupt Latency | 52 |

| 5.5 | TMS320C55x Rules and Guidelines | 52 | |

|

| 5.5.1 | Stack Architecture | 52 |

|

| 5.5.2 | Data Models | 52 |

|

| 5.5.3 | Program Models | 53 |

|

| 5.5.4 | Relocatability | 53 |

|

| 5.5.5 | Register Conventions | 54 |

|

| 5.5.6 | Status Bits | 55 |

| 5.6 | TMS320C24xx Guidelines | 57 | |

|

| 5.6.1 | General | 57 |

|

| 5.6.2 | Data Models | 57 |

|

| 5.6.3 | Program Models | 57 |

|

| 5.6.4 | Register Conventions | 57 |

|

| 5.6.5 | Status Registers | 58 |

|

| 5.6.6 | Interrupt Latency | 58 |

| 5.7 | TMS320C28x Rules and Guidelines | 58 | |

|

| 5.7.1 | Data Models | 58 |

|

| 5.7.2 | Program Models | 59 |

|

| 5.7.3 | Register Conventions | 59 |

|

| 5.7.4 | Status Registers | 59 |

|

| 5.7.5 | Interrupt Latency | 60 |

| 6 | Use of the DMA Resource | .......................................................................................... 61 | |

|

| 6.1 | Overview | 62 |

4 | Contents |

| SPRU352G | |