www.ti.com

C55x Specific DMA Rules and Guidelines

DMA Rule 7 is a rule for the client application writer. For external memory buffers that are acquired using DMA transfers, the corresponding cache entries must be invalidated to ensure that they are not cached. For buffers that are modified using CPU accesses, the corresponding cache entries must first be written back to external memory and then invalidated to ensure cache coherency.

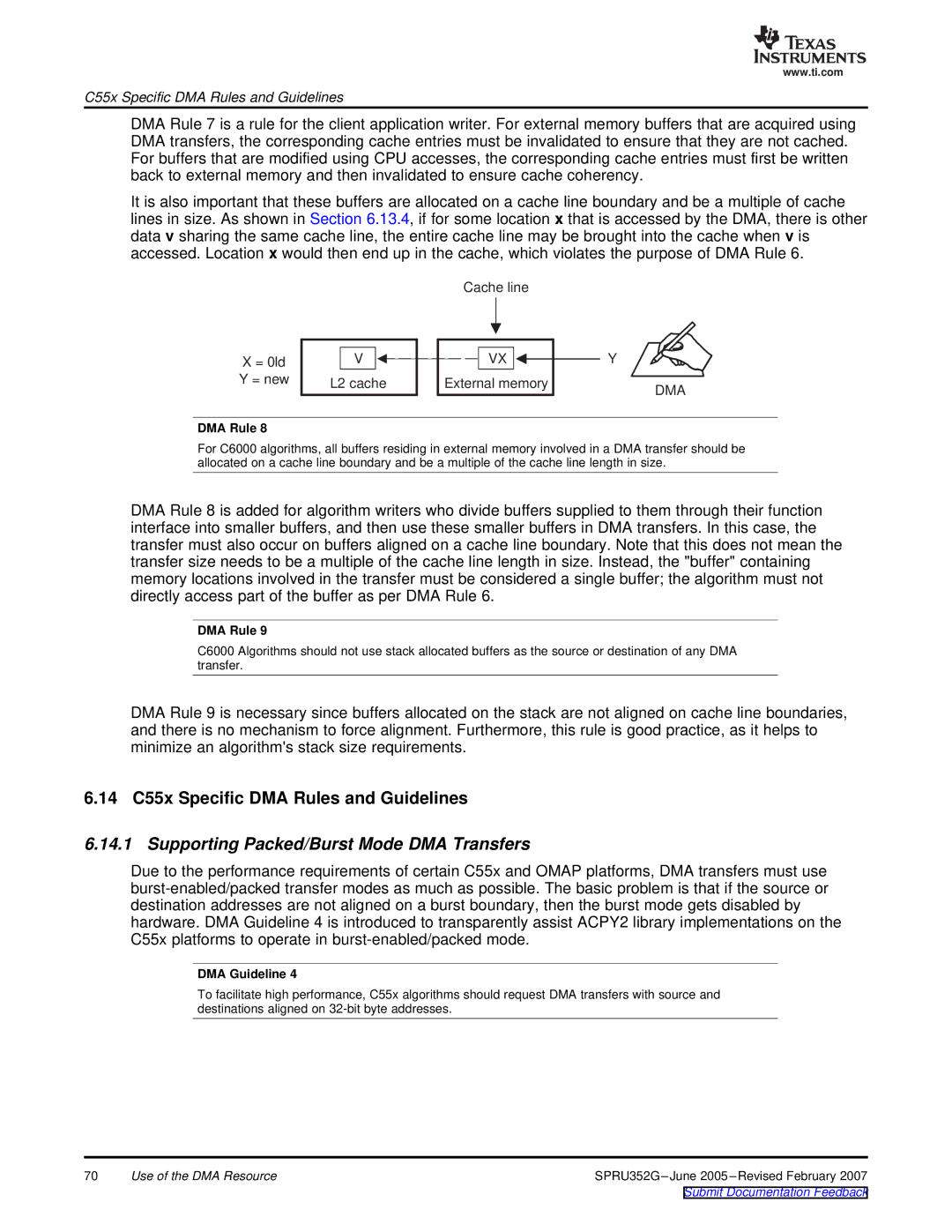

It is also important that these buffers are allocated on a cache line boundary and be a multiple of cache lines in size. As shown in Section 6.13.4, if for some location x that is accessed by the DMA, there is other data v sharing the same cache line, the entire cache line may be brought into the cache when v is accessed. Location x would then end up in the cache, which violates the purpose of DMA Rule 6.

Cache line

X = 0ld Y = new

V

L2 cache

VX ![]()

![]() External memory

External memory

Y![]()

![]()

DMA

DMA Rule 8

For C6000 algorithms, all buffers residing in external memory involved in a DMA transfer should be allocated on a cache line boundary and be a multiple of the cache line length in size.

DMA Rule 8 is added for algorithm writers who divide buffers supplied to them through their function interface into smaller buffers, and then use these smaller buffers in DMA transfers. In this case, the transfer must also occur on buffers aligned on a cache line boundary. Note that this does not mean the transfer size needs to be a multiple of the cache line length in size. Instead, the "buffer" containing memory locations involved in the transfer must be considered a single buffer; the algorithm must not directly access part of the buffer as per DMA Rule 6.

DMA Rule 9

C6000 Algorithms should not use stack allocated buffers as the source or destination of any DMA transfer.

DMA Rule 9 is necessary since buffers allocated on the stack are not aligned on cache line boundaries, and there is no mechanism to force alignment. Furthermore, this rule is good practice, as it helps to minimize an algorithm'sstack size requirements.

6.14 C55x Specific DMA Rules and Guidelines

6.14.1 Supporting Packed/Burst Mode DMA Transfers

Due to the performance requirements of certain C55x and OMAP platforms, DMA transfers must use

DMA Guideline 4

To facilitate high performance, C55x algorithms should request DMA transfers with source and destinations aligned on

70 | Use of the DMA Resource | SPRU352G |