www.ti.com

algorithm. Events

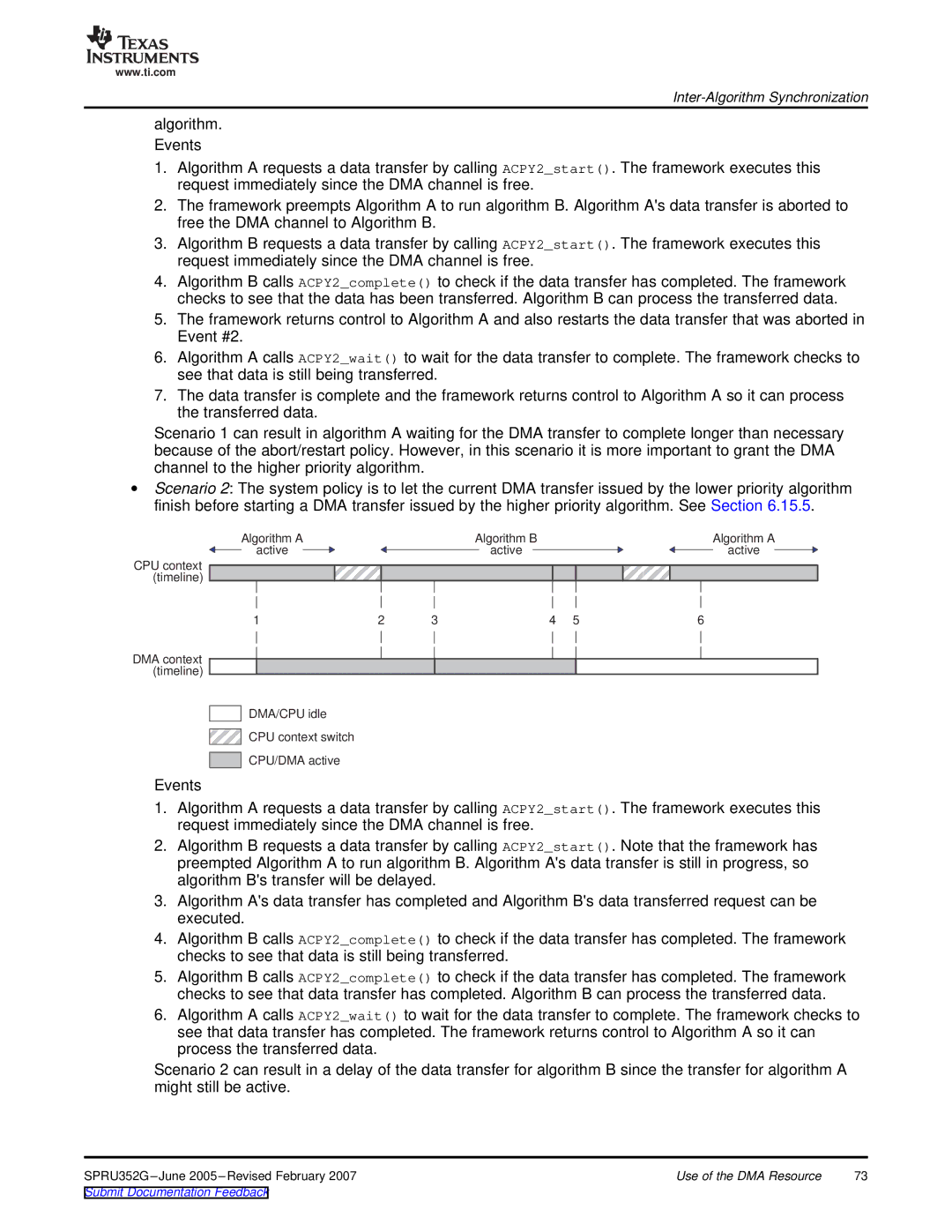

1.Algorithm A requests a data transfer by calling ACPY2_start(). The framework executes this request immediately since the DMA channel is free.

2.The framework preempts Algorithm A to run algorithm B. Algorithm A'sdata transfer is aborted to free the DMA channel to Algorithm B.

3.Algorithm B requests a data transfer by calling ACPY2_start(). The framework executes this request immediately since the DMA channel is free.

4.Algorithm B calls ACPY2_complete() to check if the data transfer has completed. The framework checks to see that the data has been transferred. Algorithm B can process the transferred data.

5.The framework returns control to Algorithm A and also restarts the data transfer that was aborted in Event #2.

6.Algorithm A calls ACPY2_wait() to wait for the data transfer to complete. The framework checks to see that data is still being transferred.

7.The data transfer is complete and the framework returns control to Algorithm A so it can process the transferred data.

Scenario 1 can result in algorithm A waiting for the DMA transfer to complete longer than necessary because of the abort/restart policy. However, in this scenario it is more important to grant the DMA channel to the higher priority algorithm.

∙Scenario 2: The system policy is to let the current DMA transfer issued by the lower priority algorithm finish before starting a DMA transfer issued by the higher priority algorithm. See Section 6.15.5.

Algorithm A |

|

| Algorithm B |

| Algorithm A |

active |

|

| active |

| active |

CPU context |

|

|

|

|

|

(timeline) |

|

|

|

|

|

1 | 2 | 3 | 4 | 5 | 6 |

DMA context |

|

|

|

|

|

(timeline) |

|

|

|

|

|

DMA/CPU idle

CPU context switch

CPU/DMA active

Events

1.Algorithm A requests a data transfer by calling ACPY2_start(). The framework executes this request immediately since the DMA channel is free.

2.Algorithm B requests a data transfer by calling ACPY2_start(). Note that the framework has preempted Algorithm A to run algorithm B. Algorithm A'sdata transfer is still in progress, so algorithm B'stransfer will be delayed.

3.Algorithm A'sdata transfer has completed and Algorithm B'sdata transferred request can be executed.

4.Algorithm B calls ACPY2_complete() to check if the data transfer has completed. The framework checks to see that data is still being transferred.

5.Algorithm B calls ACPY2_complete() to check if the data transfer has completed. The framework checks to see that data transfer has completed. Algorithm B can process the transferred data.

6.Algorithm A calls ACPY2_wait() to wait for the data transfer to complete. The framework checks to see that data transfer has completed. The framework returns control to Algorithm A so it can process the transferred data.

Scenario 2 can result in a delay of the data transfer for algorithm B since the transfer for algorithm A might still be active.

SPRU352G | Use of the DMA Resource | 73 |