www.ti.com

TMS320C28x Rules and Guidelines

Register | Use | Type |

AR6 - AR7 | C compiler Register variables | Yes |

Accumulator | Expression analysis/ return values from a C function | Preserve(local) |

P | Resulting Product from a Multiply | Scratch(local) |

T | Multiply and shift operand | Scratch(local) |

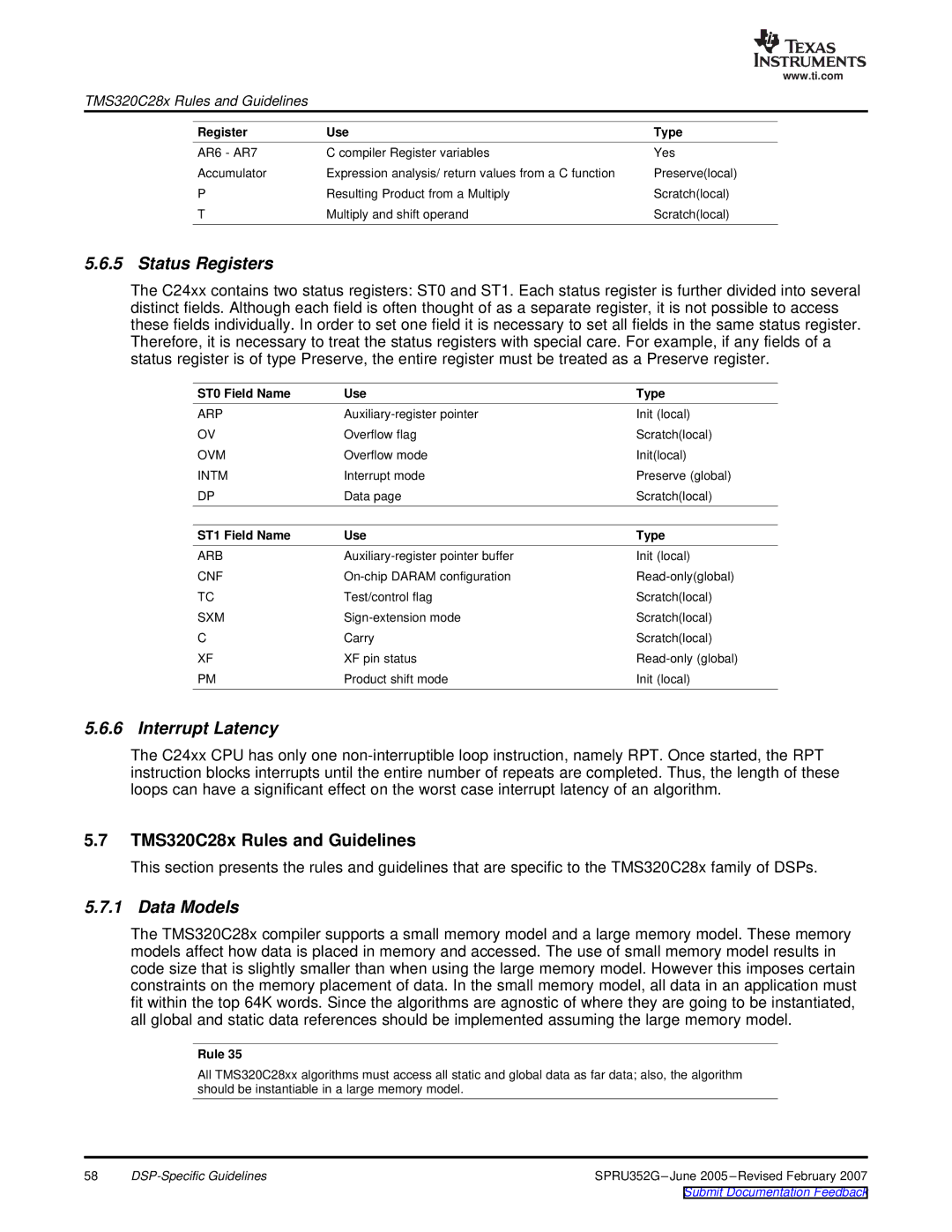

5.6.5 Status Registers

The C24xx contains two status registers: ST0 and ST1. Each status register is further divided into several distinct fields. Although each field is often thought of as a separate register, it is not possible to access these fields individually. In order to set one field it is necessary to set all fields in the same status register. Therefore, it is necessary to treat the status registers with special care. For example, if any fields of a status register is of type Preserve, the entire register must be treated as a Preserve register.

ST0 Field Name | Use | Type |

ARP | Init (local) | |

OV | Overflow flag | Scratch(local) |

OVM | Overflow mode | Init(local) |

INTM | Interrupt mode | Preserve (global) |

DP | Data page | Scratch(local) |

ST1 Field Name | Use | Type |

ARB | Init (local) | |

CNF | ||

TC | Test/control flag | Scratch(local) |

SXM | Scratch(local) | |

C | Carry | Scratch(local) |

XF | XF pin status | |

PM | Product shift mode | Init (local) |

5.6.6 Interrupt Latency

The C24xx CPU has only one

5.7TMS320C28x Rules and Guidelines

This section presents the rules and guidelines that are specific to the TMS320C28x family of DSPs.

5.7.1 Data Models

The TMS320C28x compiler supports a small memory model and a large memory model. These memory models affect how data is placed in memory and accessed. The use of small memory model results in code size that is slightly smaller than when using the large memory model. However this imposes certain constraints on the memory placement of data. In the small memory model, all data in an application must fit within the top 64K words. Since the algorithms are agnostic of where they are going to be instantiated, all global and static data references should be implemented assuming the large memory model.

Rule 35

All TMS320C28xx algorithms must access all static and global data as far data; also, the algorithm should be instantiable in a large memory model.

58 | SPRU352G |