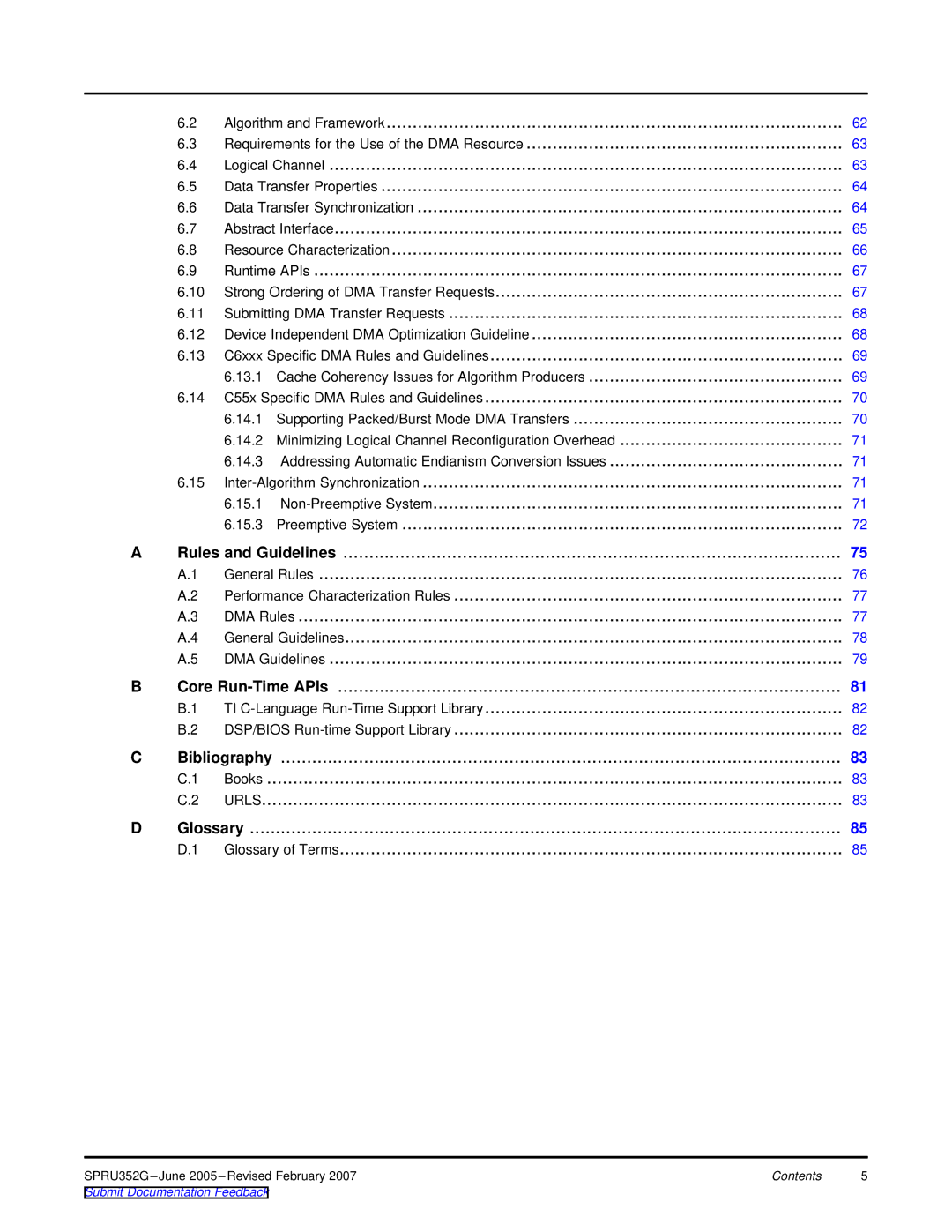

| 6.2 | Algorithm and Framework | 62 | |

| 6.3 | Requirements for the Use of the DMA Resource | 63 | |

| 6.4 | Logical Channel | 63 | |

| 6.5 | Data Transfer Properties | 64 | |

| 6.6 | Data Transfer Synchronization | 64 | |

| 6.7 | Abstract Interface | 65 | |

| 6.8 | Resource Characterization | 66 | |

| 6.9 | Runtime APIs | 67 | |

| 6.10 | Strong Ordering of DMA Transfer Requests | 67 | |

| 6.11 | Submitting DMA Transfer Requests | 68 | |

| 6.12 | Device Independent DMA Optimization Guideline | 68 | |

| 6.13 | C6xxx Specific DMA Rules and Guidelines | 69 | |

|

| 6.13.1 Cache Coherency Issues for Algorithm Producers | 69 | |

| 6.14 | C55x Specific DMA Rules and Guidelines | 70 | |

|

| 6.14.1 Supporting Packed/Burst Mode DMA Transfers | 70 | |

|

| 6.14.2 Minimizing Logical Channel Reconfiguration Overhead | 71 | |

|

| 6.14.3 Addressing Automatic Endianism Conversion Issues | 71 | |

| 6.15 | 71 | ||

|

| 6.15.1 | 71 | |

|

| 6.15.3 | Preemptive System | 72 |

A | Rules and Guidelines | 75 | ||

| A.1 | General Rules | 76 | |

| A.2 | Performance Characterization Rules | 77 | |

| A.3 | DMA Rules | 77 | |

| A.4 | General Guidelines | 78 | |

| A.5 | DMA Guidelines | 79 | |

B | Core | 81 | ||

| B.1 | TI | 82 | |

| B.2 | DSP/BIOS | 82 | |

C | Bibliography | ............................................................................................................ | 83 | |

| C.1 | Books | 83 | |

| C.2 | URLS | 83 | |

D | Glossary | 85 | ||

| D.1 | Glossary of Terms | 85 | |

SPRU352G | Contents | 5 |