www.ti.com

TMS320C28x Rules and Guidelines

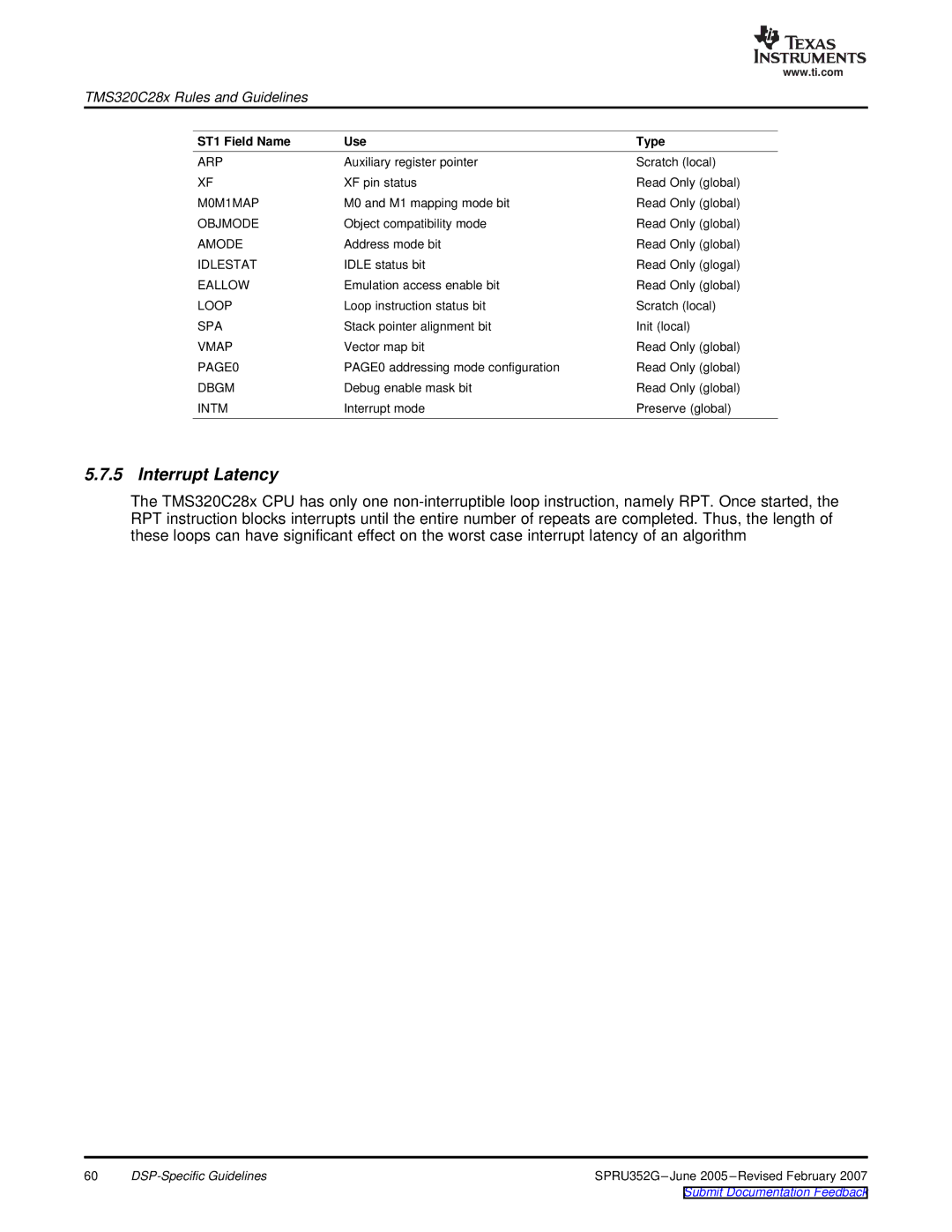

ST1 Field Name | Use | Type |

ARP | Auxiliary register pointer | Scratch (local) |

XF | XF pin status | Read Only (global) |

M0M1MAP | M0 and M1 mapping mode bit | Read Only (global) |

OBJMODE | Object compatibility mode | Read Only (global) |

AMODE | Address mode bit | Read Only (global) |

IDLESTAT | IDLE status bit | Read Only (glogal) |

EALLOW | Emulation access enable bit | Read Only (global) |

LOOP | Loop instruction status bit | Scratch (local) |

SPA | Stack pointer alignment bit | Init (local) |

VMAP | Vector map bit | Read Only (global) |

PAGE0 | PAGE0 addressing mode configuration | Read Only (global) |

DBGM | Debug enable mask bit | Read Only (global) |

INTM | Interrupt mode | Preserve (global) |

5.7.5 Interrupt Latency

The TMS320C28x CPU has only one

60 | SPRU352G |