www.ti.com

Data Transfer Properties

Some systems might map each logical channel to a physical channel, while in other systems, several logical channels map to the same physical channel. This mapping is dependent on the particular system and the number of available physical DMA channels. The important point to be made is that these variables are transparent from the algorithm'spoint of view when working with logical channels.

6.5Data Transfer Properties

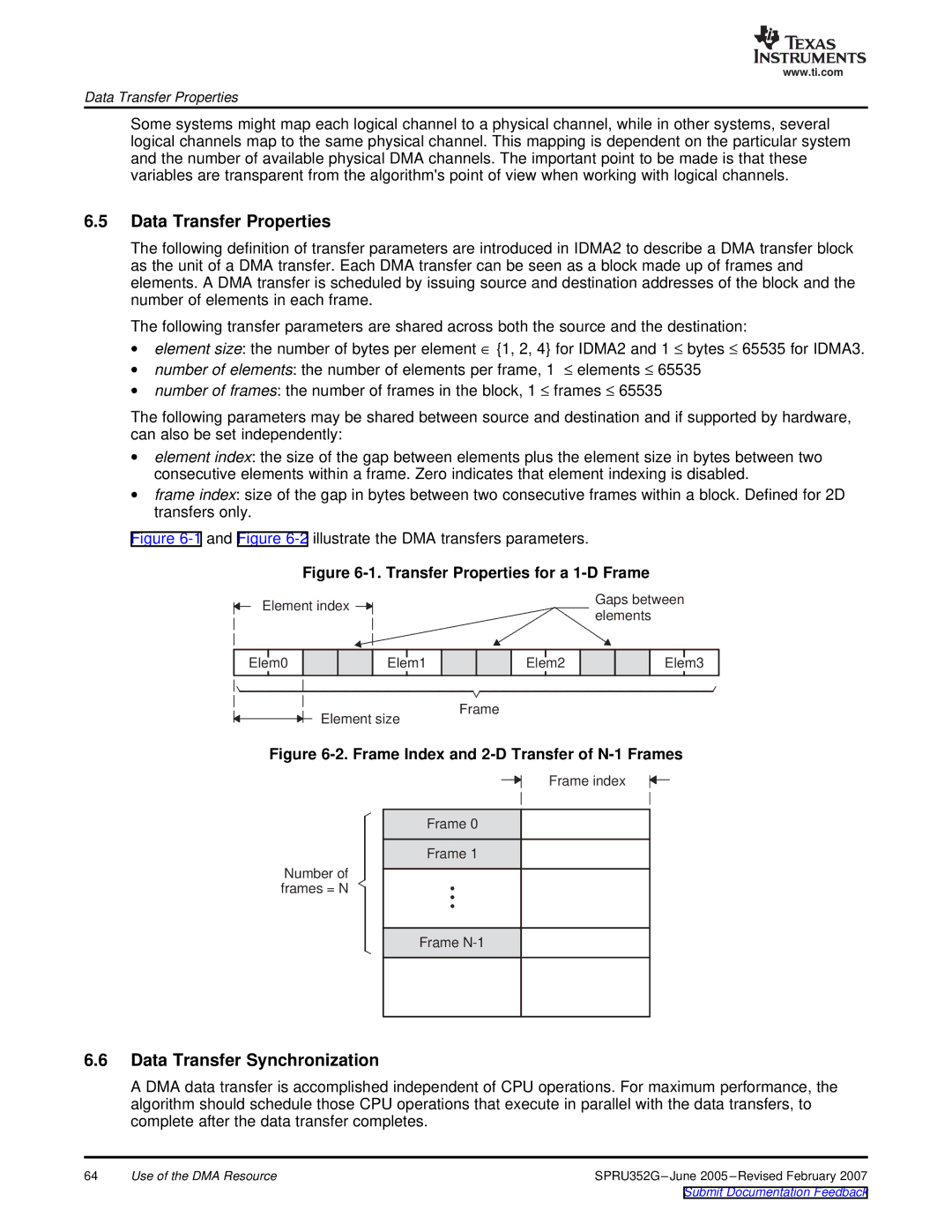

The following definition of transfer parameters are introduced in IDMA2 to describe a DMA transfer block as the unit of a DMA transfer. Each DMA transfer can be seen as a block made up of frames and elements. A DMA transfer is scheduled by issuing source and destination addresses of the block and the number of elements in each frame.

The following transfer parameters are shared across both the source and the destination:

∙element size: the number of bytes per element ∈ {1, 2, 4} for IDMA2 and 1 ≤ bytes ≤ 65535 for IDMA3.

∙number of elements: the number of elements per frame, 1 ≤ elements ≤ 65535

∙number of frames: the number of frames in the block, 1 ≤ frames ≤ 65535

The following parameters may be shared between source and destination and if supported by hardware, can also be set independently:

∙element index: the size of the gap between elements plus the element size in bytes between two consecutive elements within a frame. Zero indicates that element indexing is disabled.

∙frame index: size of the gap in bytes between two consecutive frames within a block. Defined for 2D transfers only.

Figure 6-1 and Figure 6-2 illustrate the DMA transfers parameters.

Figure 6-1. Transfer Properties for a 1-D Frame

Element index | Gaps between | |

elements | ||

|

Elem0

Elem1

Elem2

Elem3

Element size

Frame

Figure 6-2. Frame Index and 2-D Transfer of N-1 Frames

Number of frames = N

Frame index

Frame 0

Frame 1

Frame

6.6Data Transfer Synchronization

A DMA data transfer is accomplished independent of CPU operations. For maximum performance, the algorithm should schedule those CPU operations that execute in parallel with the data transfers, to complete after the data transfer completes.

64 | Use of the DMA Resource | SPRU352G |