www.ti.com

TMS320C24xx Guidelines

5.6TMS320C24xx Guidelines

This section describes the rules and guidelines that are specific to the TMS320C24xx family of digital signal processors (DSPs). Note that 24xx here refers to the following DSPs: C240, C241, C242, C243, and C240x.

5.6.1 General

As per all other

TMS320 DSP Standard Algorithms vs. DCS Modules The C24xx family of DSPs are classified as DSP controllers, and consequently are mainly focused on the ªDigital Control Space.º From an algorithm standpoint, the control space is characterized by systems built up from many smaller and reusable software blocks or modules; e.g., PID controllers, coordinate transformations, trigonometric transformations, signal generators, etc. In addition, the C24xx DSP controllers are offered in numerous memory configurations, with lower cost devices having 4k words of program memory. This imposes some restrictions on how much overhead can be wrapped on each one of these smaller modules when creating it's interface, or API.

In order to address the mentioned sensitivities within the control space, the Digital Control Systems group (DCS) at TI has created smaller and reusable blocks of modular software known as DCS modules. These modules are not

Please refer to the application note, SPRA701, A Software Modularity Strategy for

Digital Control Systems, for further information on DCS modules.

5.6.2 Data Models

The C24xx has just one data model, so there are no special data memory requirements for this processor.

5.6.3 Program Models

The C24xx C compiler supports only the one standard 64K word reach program model, so there are no special program memory requirements for this processor.

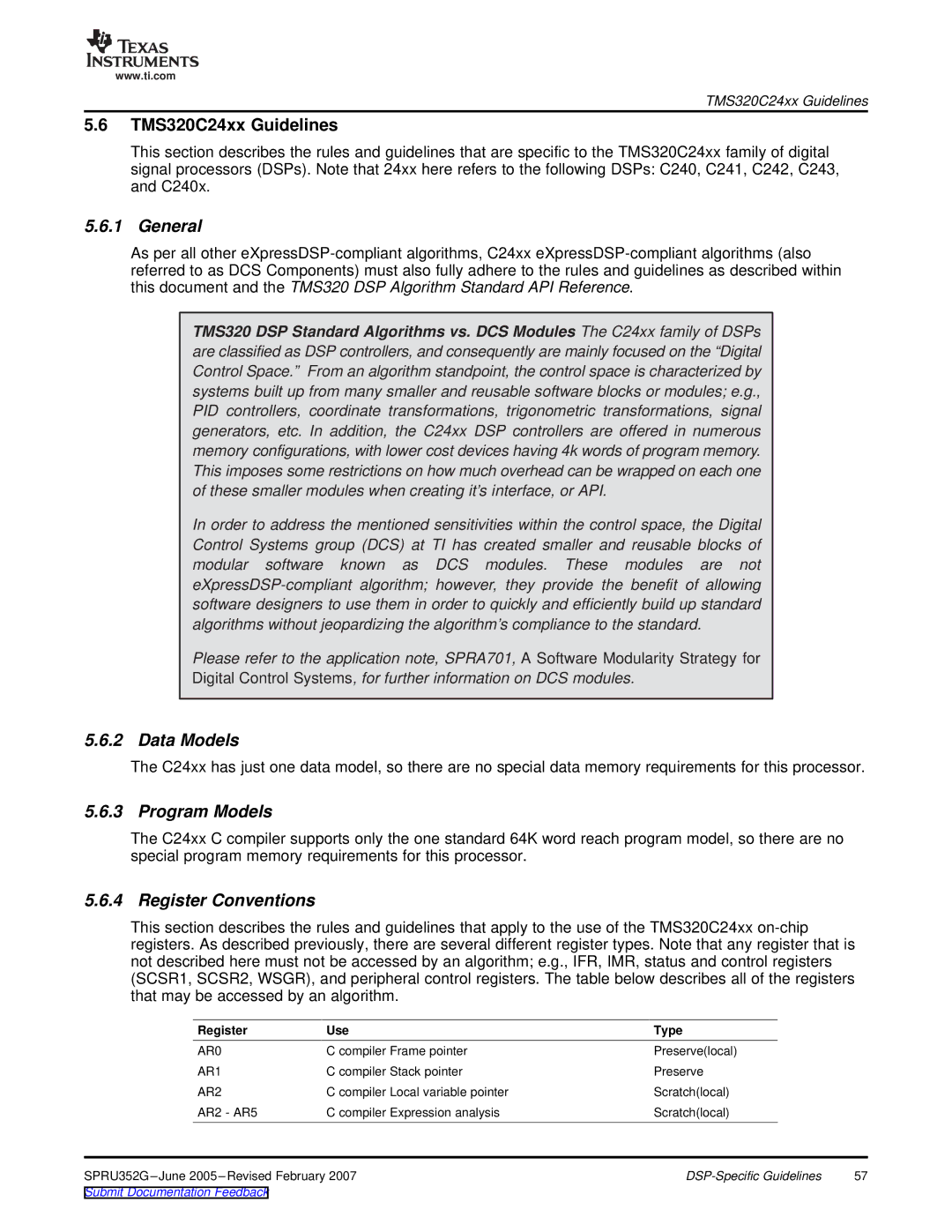

5.6.4 Register Conventions

This section describes the rules and guidelines that apply to the use of the TMS320C24xx

Register | Use | Type |

|

AR0 | C compiler Frame pointer | Preserve(local) |

|

AR1 | C compiler Stack pointer | Preserve |

|

AR2 | C compiler Local variable pointer | Scratch(local) |

|

AR2 - AR5 | C compiler Expression analysis | Scratch(local) |

|

SPRU352G | 57 | ||

Submit Documentation Feedback |

|

|

|