www.ti.com

TMS320C54xx Rules and Guidelines

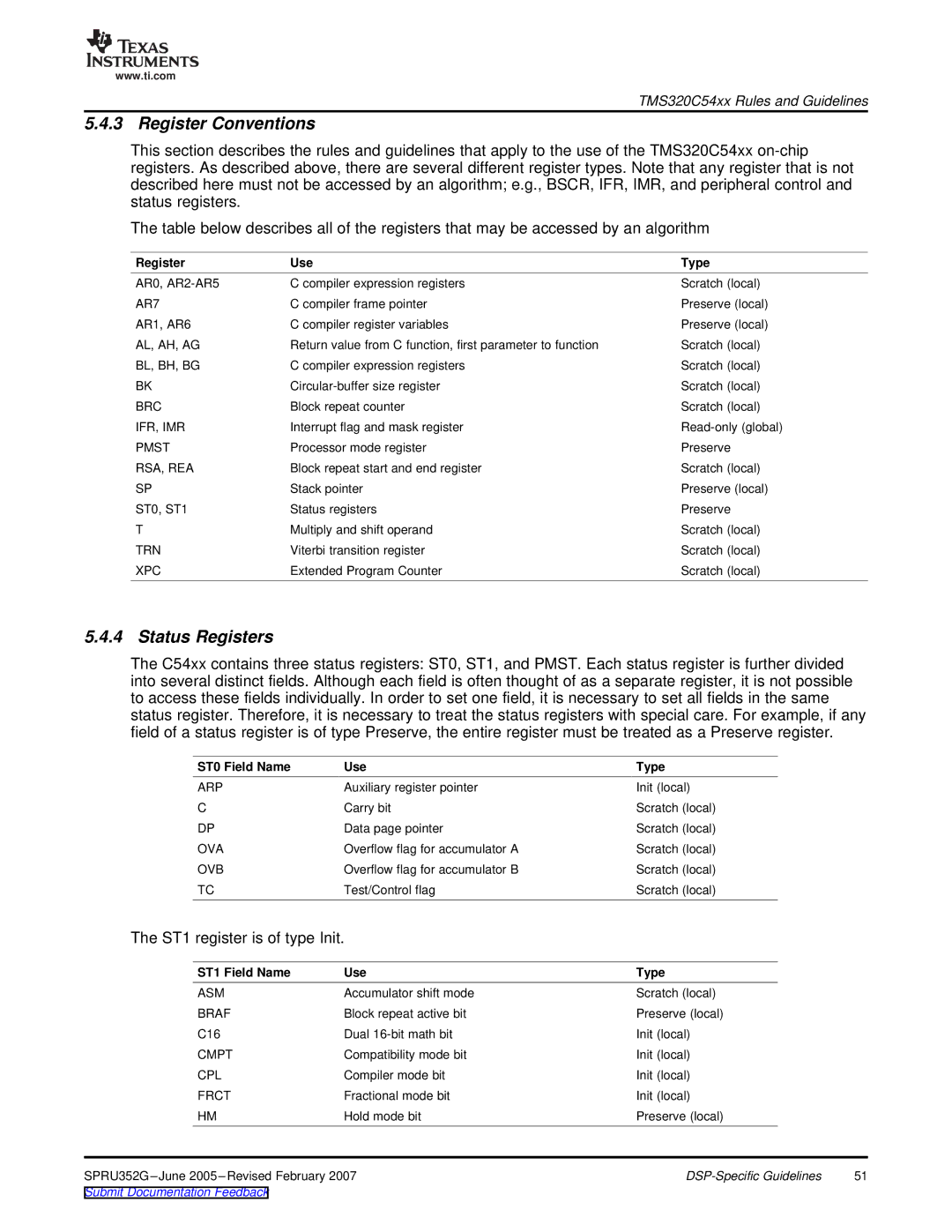

5.4.3 Register Conventions

This section describes the rules and guidelines that apply to the use of the TMS320C54xx

The table below describes all of the registers that may be accessed by an algorithm

Register | Use | Type |

AR0, | C compiler expression registers | Scratch (local) |

AR7 | C compiler frame pointer | Preserve (local) |

AR1, AR6 | C compiler register variables | Preserve (local) |

AL, AH, AG | Return value from C function, first parameter to function | Scratch (local) |

BL, BH, BG | C compiler expression registers | Scratch (local) |

BK | Scratch (local) | |

BRC | Block repeat counter | Scratch (local) |

IFR, IMR | Interrupt flag and mask register | |

PMST | Processor mode register | Preserve |

RSA, REA | Block repeat start and end register | Scratch (local) |

SP | Stack pointer | Preserve (local) |

ST0, ST1 | Status registers | Preserve |

T | Multiply and shift operand | Scratch (local) |

TRN | Viterbi transition register | Scratch (local) |

XPC | Extended Program Counter | Scratch (local) |

5.4.4 Status Registers

The C54xx contains three status registers: ST0, ST1, and PMST. Each status register is further divided into several distinct fields. Although each field is often thought of as a separate register, it is not possible to access these fields individually. In order to set one field, it is necessary to set all fields in the same status register. Therefore, it is necessary to treat the status registers with special care. For example, if any field of a status register is of type Preserve, the entire register must be treated as a Preserve register.

ST0 Field Name | Use | Type |

ARP | Auxiliary register pointer | Init (local) |

C | Carry bit | Scratch (local) |

DP | Data page pointer | Scratch (local) |

OVA | Overflow flag for accumulator A | Scratch (local) |

OVB | Overflow flag for accumulator B | Scratch (local) |

TC | Test/Control flag | Scratch (local) |

The ST1 register is of type Init.

ST1 Field Name | Use | Type |

|

ASM | Accumulator shift mode | Scratch (local) |

|

BRAF | Block repeat active bit | Preserve (local) |

|

C16 | Dual | Init (local) |

|

CMPT | Compatibility mode bit | Init (local) |

|

CPL | Compiler mode bit | Init (local) |

|

FRCT | Fractional mode bit | Init (local) |

|

HM | Hold mode bit | Preserve (local) |

|

SPRU352G | 51 | ||

Submit Documentation Feedback |

|

|

|