www.ti.com

Supported Use Cases

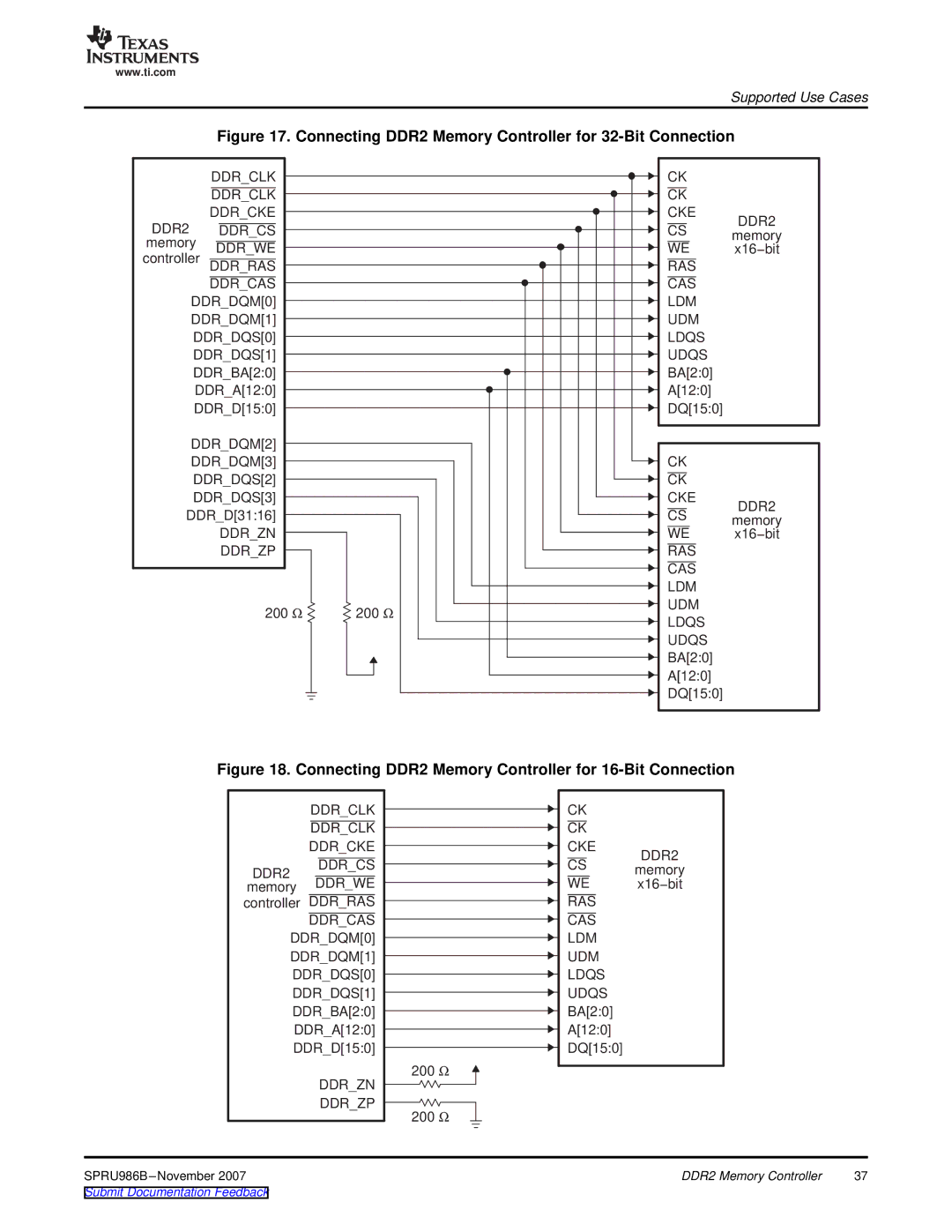

Figure 17. Connecting DDR2 Memory Controller for 32-Bit Connection

| DDR_CLK |

|

| DDR_CLK |

|

| DDR_CKE |

|

DDR2 | DDR_CS |

|

memory | DDR_WE |

|

controller |

| |

DDR_RAS |

| |

| DDR_CAS |

|

DDR_DQM[0] |

| |

DDR_DQM[1] |

| |

DDR_DQS[0] |

| |

DDR_DQS[1] |

| |

DDR_BA[2:0] |

| |

DDR_A[12:0] |

| |

DDR_D[15:0] |

| |

DDR_DQM[2] |

| |

DDR_DQM[3] |

| |

DDR_DQS[2] |

| |

DDR_DQS[3] |

| |

DDR_D[31:16] |

| |

| DDR_ZN |

|

| DDR_ZP |

|

| 200 Ω | 200 Ω |

CK

CK

CKE

DDR2

CS memory

WE x16−bit

RAS

CAS

LDM

UDM

LDQS

UDQS

BA[2:0]

A[12:0]

DQ[15:0]

CK

CK

CKE

DDR2

CS memory

WE x16−bit

RAS

CAS

LDM

UDM

LDQS

UDQS

BA[2:0]

A[12:0]

DQ[15:0]

Figure 18. Connecting DDR2 Memory Controller for 16-Bit Connection

DDR_CLK

DDR_CLK DDR_CKE

CK

CK

CKE

DDR2

DDR2

DDR_CS

CS memory

memory DDR_WE controller DDR_RAS

DDR_CAS

DDR_DQM[0]

DDR_DQM[1]

DDR_DQS[0]

DDR_DQS[1]

DDR_BA[2:0]

DDR_A[12:0]

DDR_D[15:0]

DDR_ZN

DDR_ZP

200Ω

200Ω

WE x16−bit

RAS

CAS

LDM

UDM

LDQS

UDQS

BA[2:0]

A[12:0]

DQ[15:0]

DDR2 Memory Controller | 37 |