www.ti.com

Peripheral Architecture

2Peripheral Architecture

This section describes the architecture of the DDR2 memory controller as well as how it is structured and how it works within the context of the

2.1Clock Control

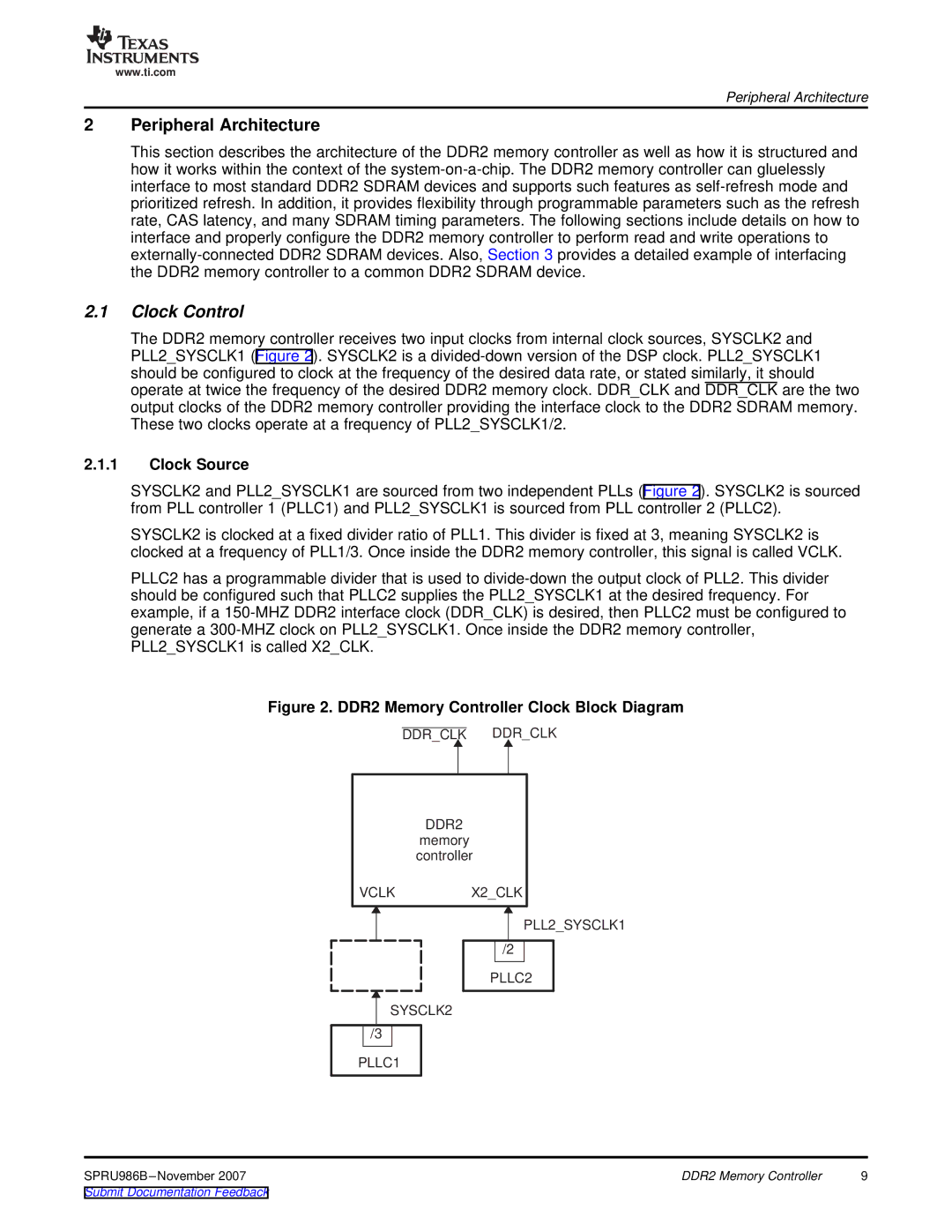

The DDR2 memory controller receives two input clocks from internal clock sources, SYSCLK2 and PLL2_SYSCLK1 (Figure 2). SYSCLK2 is a

2.1.1Clock Source

SYSCLK2 and PLL2_SYSCLK1 are sourced from two independent PLLs (Figure 2). SYSCLK2 is sourced from PLL controller 1 (PLLC1) and PLL2_SYSCLK1 is sourced from PLL controller 2 (PLLC2).

SYSCLK2 is clocked at a fixed divider ratio of PLL1. This divider is fixed at 3, meaning SYSCLK2 is clocked at a frequency of PLL1/3. Once inside the DDR2 memory controller, this signal is called VCLK.

PLLC2 has a programmable divider that is used to

Figure 2. DDR2 Memory Controller Clock Block Diagram

DDR_CLK DDR_CLK

DDR2 memory controller

VCLKX2_CLK

PLL2_SYSCLK1

/2

PLLC2

SYSCLK2

/3

PLLC1

DDR2 Memory Controller | 9 |