www.ti.com

Appendix A

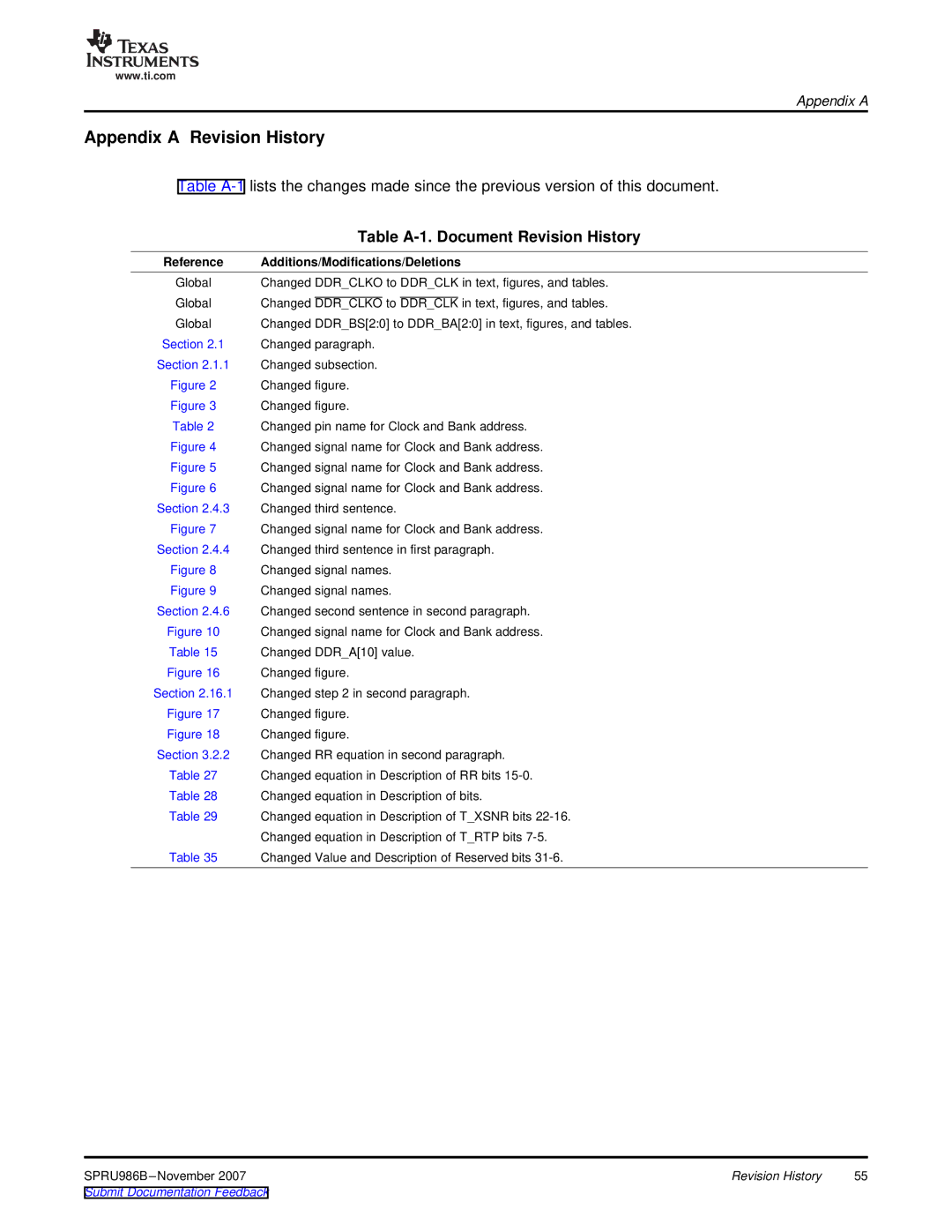

Appendix A Revision History

Table

| Table |

Reference | Additions/Modifications/Deletions |

Global | Changed DDR_CLKO to DDR_CLK in text, figures, and tables. |

Global | Changed DDR_CLKO to DDR_CLK in text, figures, and tables. |

Global | Changed DDR_BS[2:0] to DDR_BA[2:0] in text, figures, and tables. |

Section 2.1 | Changed paragraph. |

Section 2.1.1 | Changed subsection. |

Figure 2 | Changed figure. |

Figure 3 | Changed figure. |

Table 2 | Changed pin name for Clock and Bank address. |

Figure 4 | Changed signal name for Clock and Bank address. |

Figure 5 | Changed signal name for Clock and Bank address. |

Figure 6 | Changed signal name for Clock and Bank address. |

Section 2.4.3 | Changed third sentence. |

Figure 7 | Changed signal name for Clock and Bank address. |

Section 2.4.4 | Changed third sentence in first paragraph. |

Figure 8 | Changed signal names. |

Figure 9 | Changed signal names. |

Section 2.4.6 | Changed second sentence in second paragraph. |

Figure 10 | Changed signal name for Clock and Bank address. |

Table 15 | Changed DDR_A[10] value. |

Figure 16 | Changed figure. |

Section 2.16.1 | Changed step 2 in second paragraph. |

Figure 17 | Changed figure. |

Figure 18 | Changed figure. |

Section 3.2.2 | Changed RR equation in second paragraph. |

Table 27 | Changed equation in Description of RR bits |

Table 28 | Changed equation in Description of bits. |

Table 29 | Changed equation in Description of T_XSNR bits |

| Changed equation in Description of T_RTP bits |

Table 35 | Changed Value and Description of Reserved bits |

Revision History | 55 | |

Submit Documentation Feedback |

|

|