www.ti.com | Peripheral Architecture |

2.4.3Data Format

The UART transmits in the following format:

1 START bit + data bits (5, 6, 7, 8) + 1 PARITY bit (optional) + STOP bit (1, 1.5, 2)

It transmits 1 START bit; 5, 6, 7, or 8 data bits, depending on the data width selection; 1 PARITY bit, if parity is selected; and 1, 1.5, or 2 STOP bits, depending on the STOP bit selection.

The UART receives in the following format:

1 START bit + data bits (5, 6, 7, 8) + 1 PARITY bit (optional) + STOP bit (1)

It receives 1 START bit; 5, 6, 7, or 8 data bits, depending on the data width selection; 1 PARITY bit, if parity is selected; and 1 STOP bit.

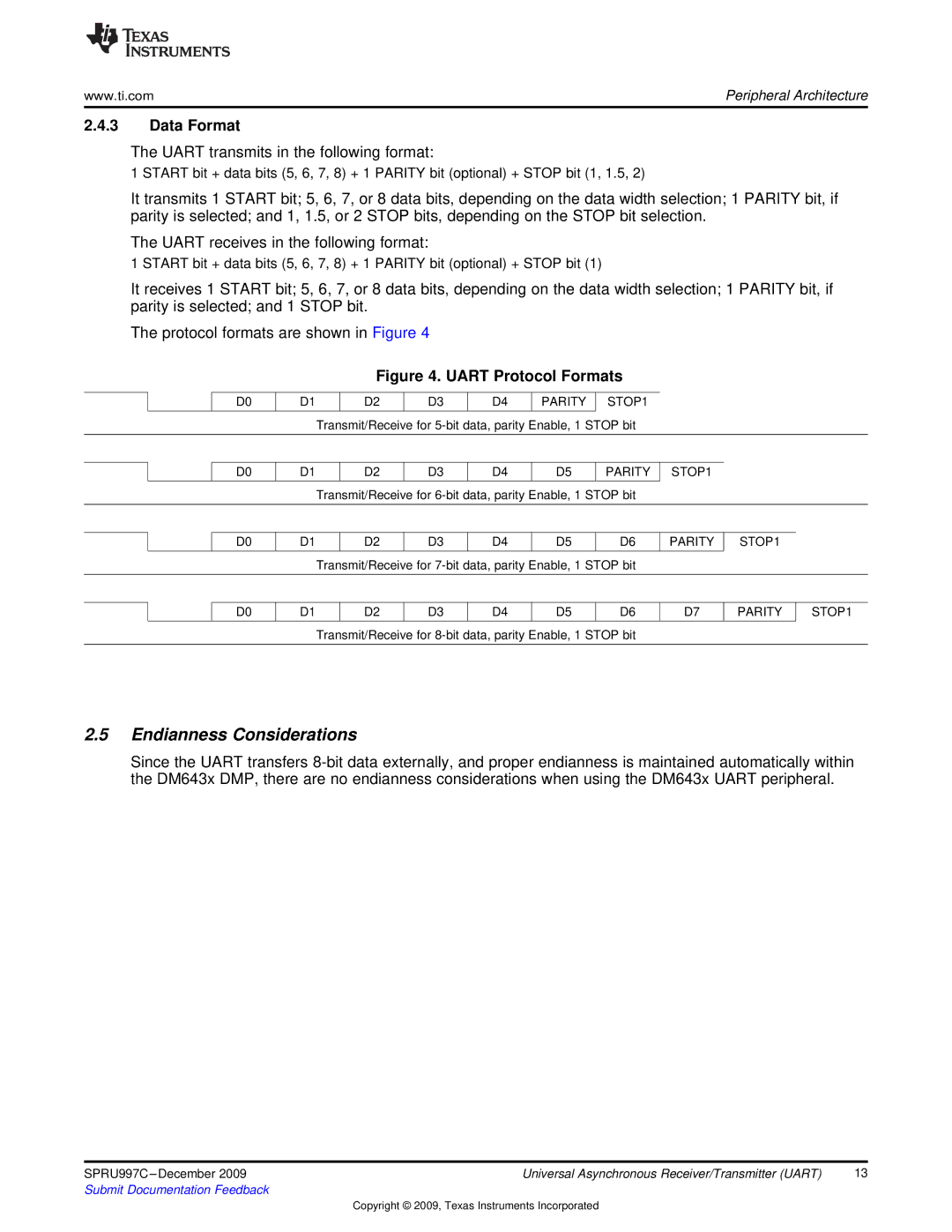

The protocol formats are shown in Figure 4

Figure 4. UART Protocol Formats

|

| D0 | D1 |

| D2 | D3 | D4 | PARITY | STOP1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Transmit/Receive for | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| D0 | D1 |

| D2 | D3 | D4 | D5 | PARITY |

|

|

|

| Transmit/Receive for | |||||

STOP1

|

| D0 | D1 |

| D2 | D3 | D4 | D5 | D6 | PARITY |

|

|

|

| Transmit/Receive for |

| |||||

STOP1

|

| D0 | D1 |

| D2 | D3 | D4 | D5 | D6 | D7 | PARITY |

|

|

|

| Transmit/Receive for |

|

| |||||

STOP1

2.5Endianness Considerations

Since the UART transfers

SPRU997C | Universal Asynchronous Receiver/Transmitter (UART) | 13 |

Submit Documentation Feedback |

|

|

Copyright © 2009, Texas Instruments Incorporated