Registers | www.ti.com |

3.1Receiver Buffer Register (RBR)

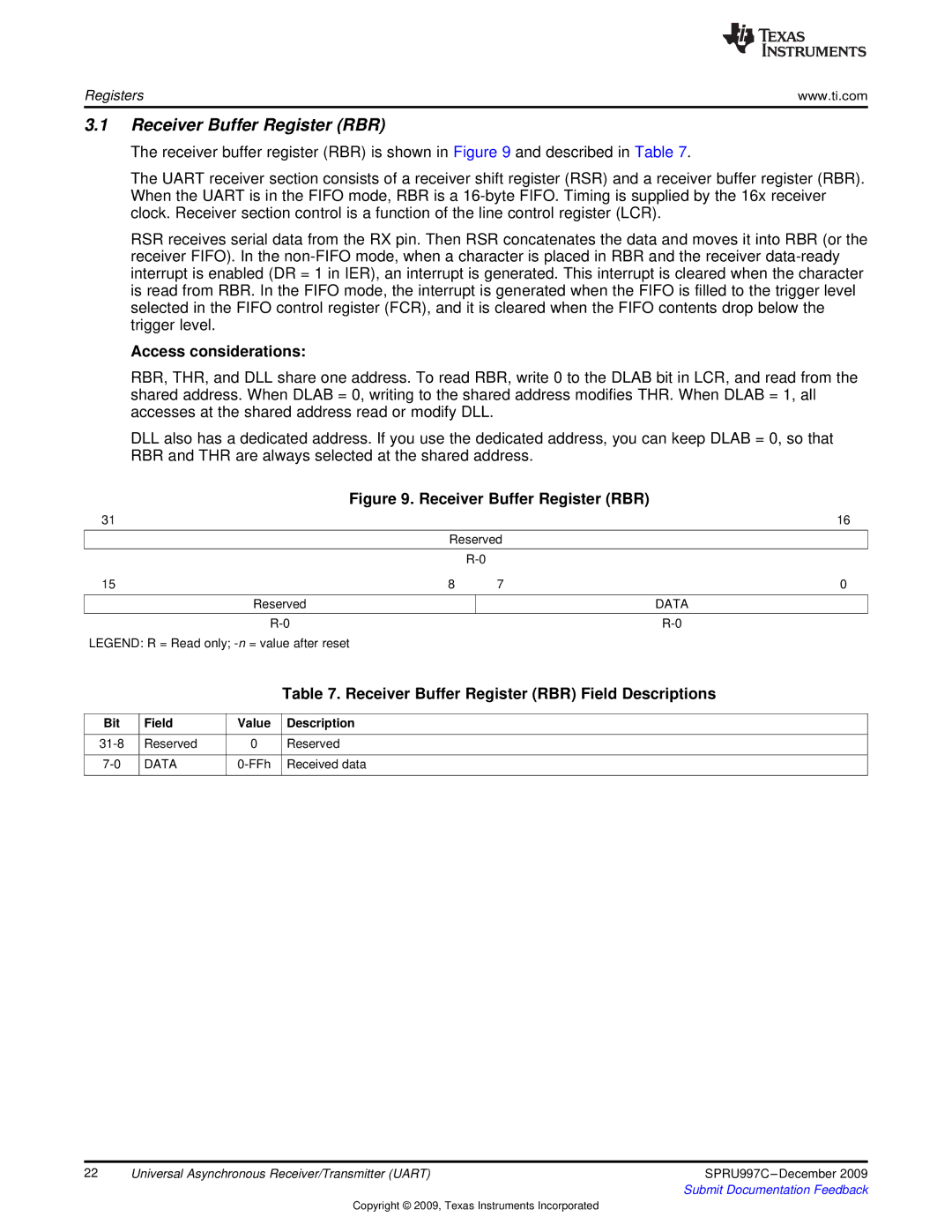

The receiver buffer register (RBR) is shown in Figure 9 and described in Table 7.

The UART receiver section consists of a receiver shift register (RSR) and a receiver buffer register (RBR). When the UART is in the FIFO mode, RBR is a

RSR receives serial data from the RX pin. Then RSR concatenates the data and moves it into RBR (or the receiver FIFO). In the

Access considerations:

RBR, THR, and DLL share one address. To read RBR, write 0 to the DLAB bit in LCR, and read from the shared address. When DLAB = 0, writing to the shared address modifies THR. When DLAB = 1, all accesses at the shared address read or modify DLL.

DLL also has a dedicated address. If you use the dedicated address, you can keep DLAB = 0, so that RBR and THR are always selected at the shared address.

Figure 9. Receiver Buffer Register (RBR)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

|

| |

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

| Reserved |

|

| DATA |

|

|

| ||

LEGEND: R = Read only;

|

|

| Table 7. Receiver Buffer Register (RBR) Field Descriptions |

|

|

|

|

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

DATA | Received data | ||

|

|

|

|

22 | Universal Asynchronous Receiver/Transmitter (UART) | SPRU997C |

|

| Submit Documentation Feedback |

Copyright © 2009, Texas Instruments Incorporated