www.ti.com | Peripheral Architecture |

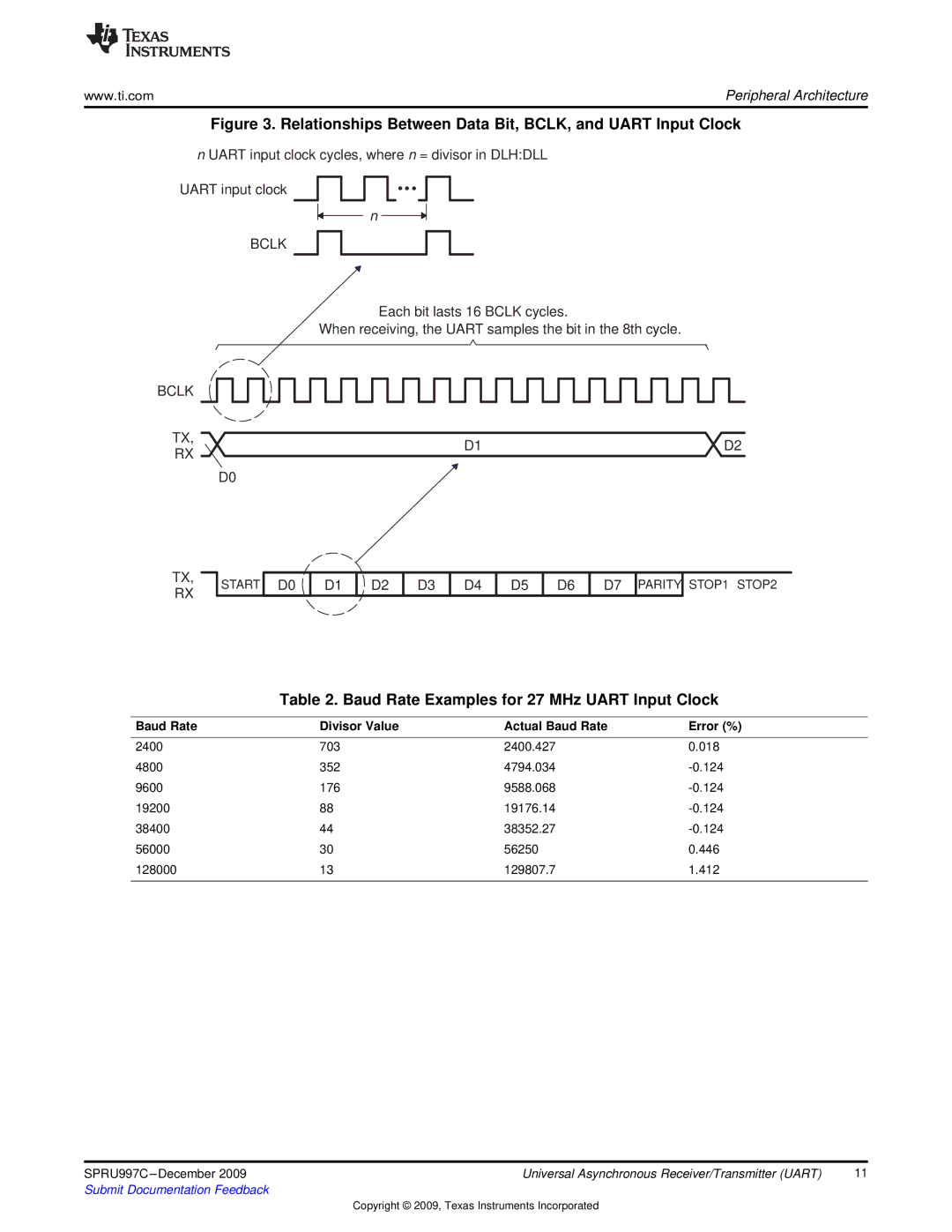

Figure 3. Relationships Between Data Bit, BCLK, and UART Input Clock

n UART input clock cycles, where n = divisor in DLH:DLL

UART input clock

n

BCLK

BCLK

TX,

RX

D0

Each bit lasts 16 BCLK cycles.

When receiving, the UART samples the bit in the 8th cycle.

D1 | D2 |

TX, | START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | PARITY STOP1 STOP2 | |

RX | |||||||||||

|

|

|

|

|

|

|

|

|

|

Table 2. Baud Rate Examples for 27 MHz UART Input Clock

Baud Rate | Divisor Value | Actual Baud Rate | Error (%) |

2400 | 703 | 2400.427 | 0.018 |

4800 | 352 | 4794.034 | |

9600 | 176 | 9588.068 | |

19200 | 88 | 19176.14 | |

38400 | 44 | 38352.27 | |

56000 | 30 | 56250 | 0.446 |

128000 | 13 | 129807.7 | 1.412 |

|

|

|

|

SPRU997C | Universal Asynchronous Receiver/Transmitter (UART) | 11 |

Submit Documentation Feedback |

|

|

Copyright © 2009, Texas Instruments Incorporated