www.ti.com | Registers |

3.2Transmitter Holding Register (THR)

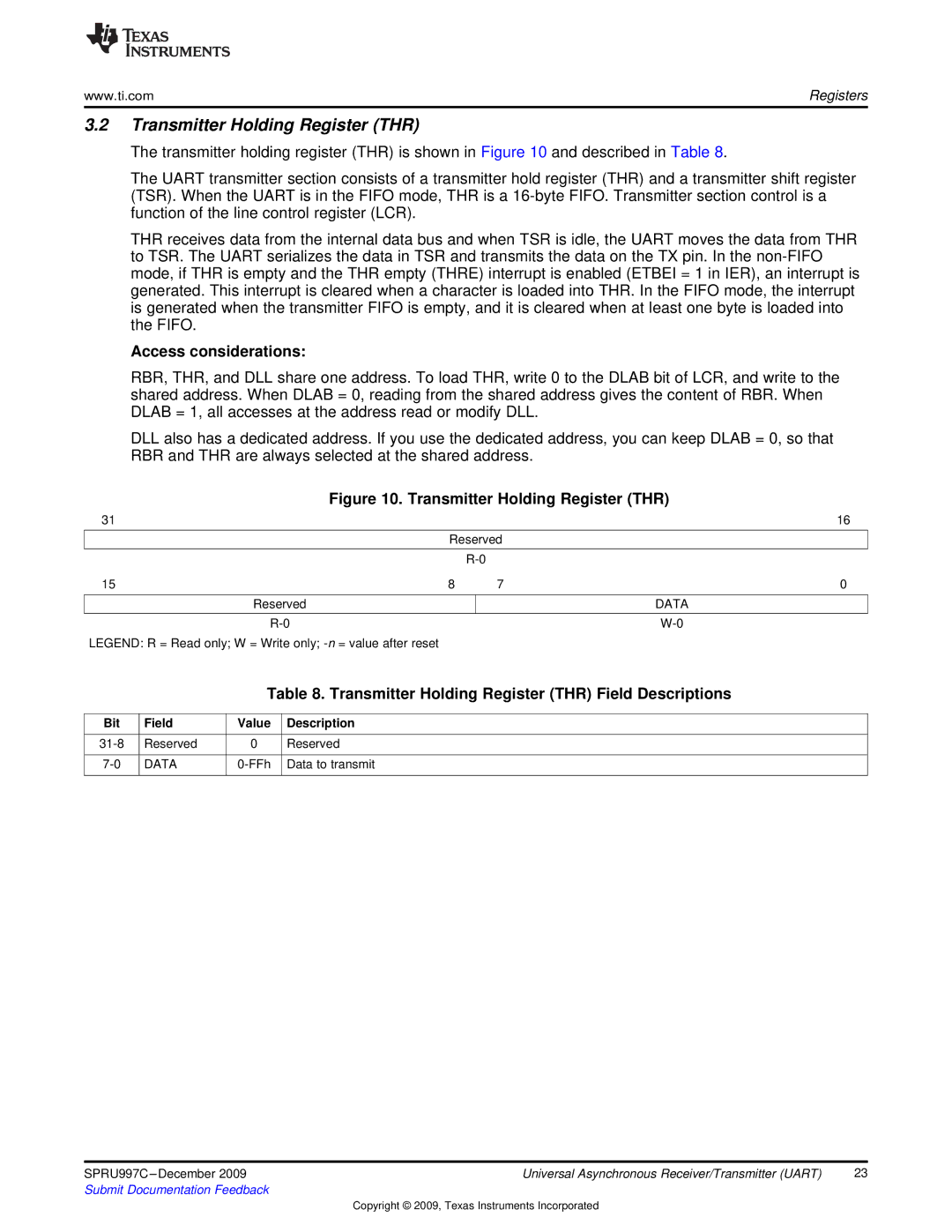

The transmitter holding register (THR) is shown in Figure 10 and described in Table 8.

The UART transmitter section consists of a transmitter hold register (THR) and a transmitter shift register (TSR). When the UART is in the FIFO mode, THR is a

THR receives data from the internal data bus and when TSR is idle, the UART moves the data from THR to TSR. The UART serializes the data in TSR and transmits the data on the TX pin. In the

Access considerations:

RBR, THR, and DLL share one address. To load THR, write 0 to the DLAB bit of LCR, and write to the shared address. When DLAB = 0, reading from the shared address gives the content of RBR. When DLAB = 1, all accesses at the address read or modify DLL.

DLL also has a dedicated address. If you use the dedicated address, you can keep DLAB = 0, so that RBR and THR are always selected at the shared address.

Figure 10. Transmitter Holding Register (THR)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

|

| |

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

| Reserved |

|

| DATA |

|

|

| ||

LEGEND: R = Read only; W = Write only;

Table 8. Transmitter Holding Register (THR) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

DATA | Data to transmit | ||

|

|

|

|

SPRU997C | Universal Asynchronous Receiver/Transmitter (UART) | 23 |

Submit Documentation Feedback |

|

|

Copyright © 2009, Texas Instruments Incorporated