Peripheral Architecture | www.ti.com |

2.6.3.2FIFO Poll Mode

When the receiver FIFO is enabled in the FIFO control register (FCR) and the receiver interrupts are disabled in the interrupt enable register (IER), the poll mode is selected for the receiver FIFO. Similarly, when the transmitter FIFO is enabled and the transmitter interrupts are disabled, the transmitted FIFO is in the poll mode. In the poll mode, the CPU detects events by checking bits in the line status register (LSR):

•The RXFIFOE bit indicates whether there are any errors in the receiver FIFO.

•The TEMT bit indicates that both the transmitter holding register (THR) and the transmitter shift register (TSR) are empty.

•The THRE bit indicates when THR is empty.

•The BI (break), FE (framing error), PE (parity error), and OE (overrun error) bits specify which error or errors have occurred.

•The DR

Also, in the FIFO poll mode:

•The interrupt identification register (IIR) is not affected by any events because the interrupts are disabled.

•The UART does not indicate when the receiver FIFO trigger level is reached or when a receiver

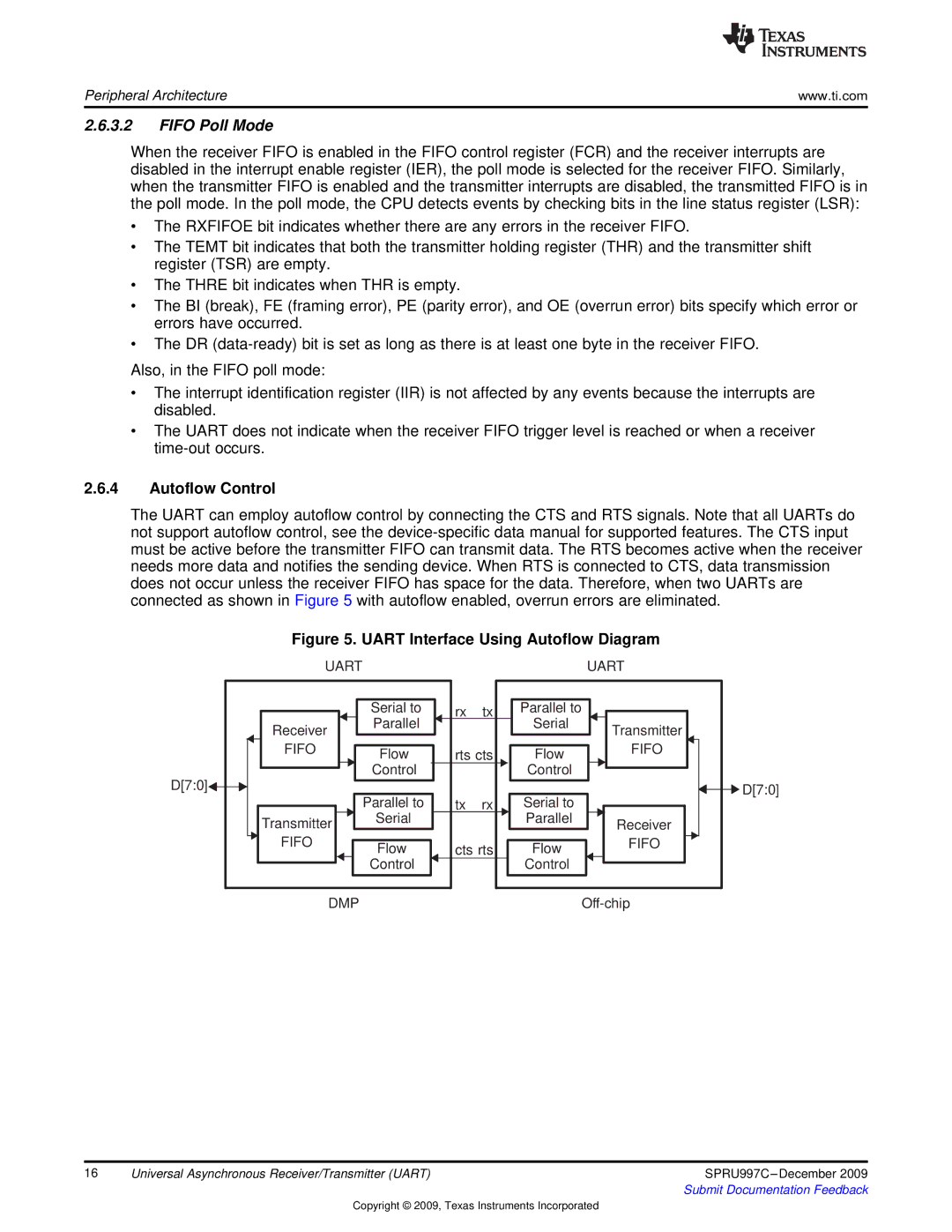

2.6.4Autoflow Control

The UART can employ autoflow control by connecting the CTS and RTS signals. Note that all UARTs do not support autoflow control, see the

Figure 5. UART Interface Using Autoflow Diagram | |||||

UART |

|

|

|

| UART |

| Serial to | rx | tx | Parallel to |

|

| Parallel | Serial |

| ||

Receiver |

|

| Transmitter | ||

|

|

|

| ||

FIFO | Flow | rts cts | Flow | FIFO | |

|

| ||||

D[7:0] | Control |

|

| Control |

|

|

|

|

| D[7:0] | |

| Parallel to | tx | rx | Serial to | |

|

| ||||

Transmitter | Serial |

|

| Parallel | Receiver |

|

|

|

| ||

FIFO | Flow | cts rts | Flow | FIFO | |

|

| ||||

| Control |

|

| Control |

|

DMP |

|

|

|

|

|

16 | Universal Asynchronous Receiver/Transmitter (UART) | SPRU997C |

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated