www.ti.com | Peripheral Architecture |

Table 5. UART Interrupt Requests Descriptions

UART Interrupt |

|

Request | Interrupt Source |

|

|

THREINT | |

| (THR) or the transmitter FIFO is empty. All of the data |

| has been copied from THR to the transmitter shift |

| register (TSR). |

RDAINT | Receive data available in |

| level reached in the FIFO mode. |

Comment

If THREINT is enabled in IER, by setting the ETBEI bit, it is recorded in IIR.

As an alternative to using THREINT, the CPU can poll the THRE bit in the line status register (LSR).

If RDAINT is enabled in IER, by setting the ERBI bit, it is recorded in IIR.

As an alternative to using RDAINT, the CPU can poll the DR bit in the line status register (LSR). In the FIFO mode, this is not a functionally equivalent alternative because the DR bit does not respond to the FIFO trigger level. The DR bit only indicates the presence or absence of unread characters.

RTOINT | Receiver |

| No characters have been removed from or input to |

| the receiver FIFO during the last four character times |

| (see Table 4), and there is at least one character in |

| the receiver FIFO during this time. |

The receiver

If RTOINT is enabled in IER, by setting the ERBI bit, it is recorded in IIR.

There is no status bit to reflect the occurrence of a

RLSINT | Receiver line status condition: An overrun error, parity |

| error, framing error, or break has occurred. |

If RLSINT is enabled in IER, by setting the ELSI bit, it is recorded in IIR.

As an alternative to using RLSINT, the CPU can poll the following bits in the line status register (LSR): overrun error indicator (OE), parity error indicator (PE), framing error indicator (FE), and break indicator (BI).

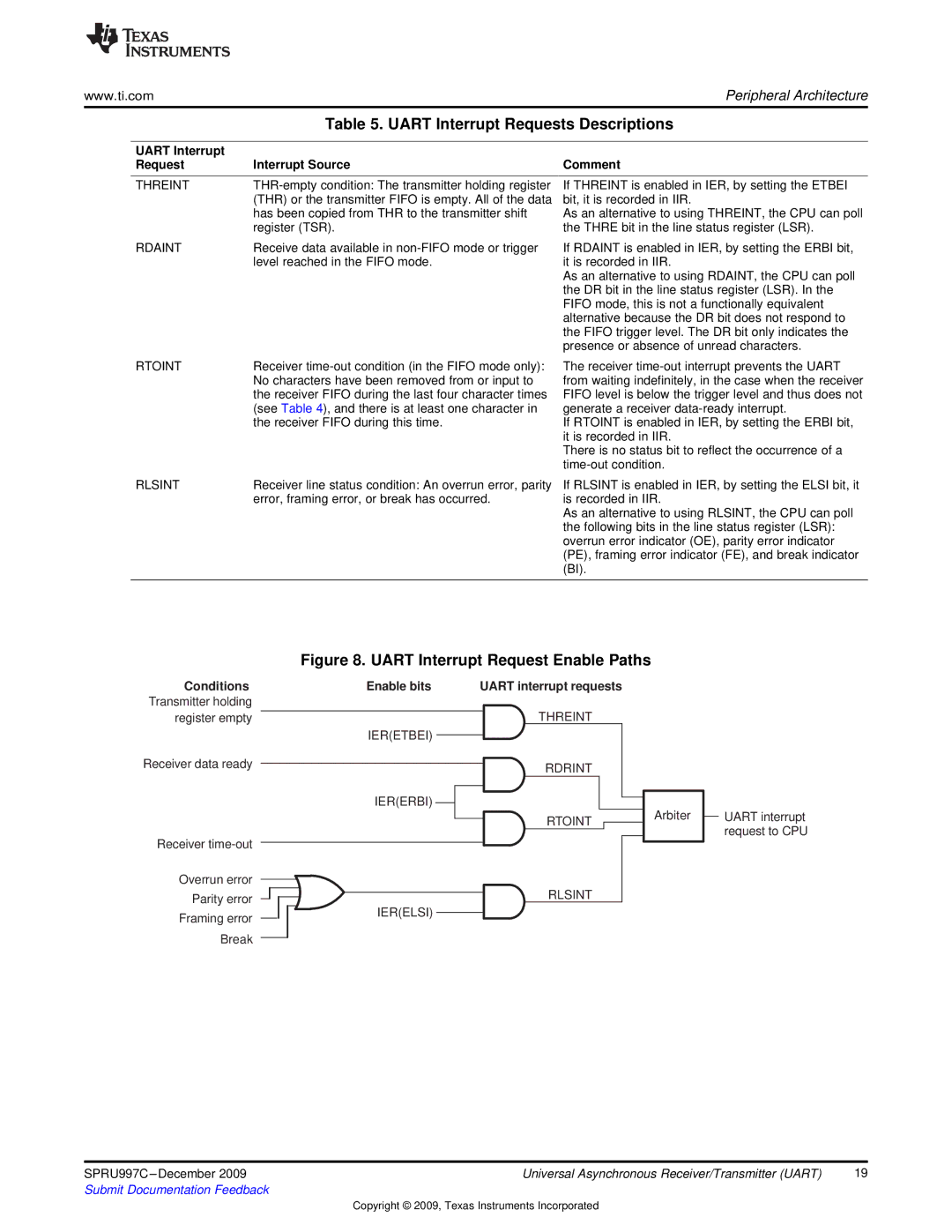

Figure 8. UART Interrupt Request Enable Paths

Conditions

Transmitter holding register empty

Receiver data ready

Receiver

Overrun error

Parity error

Framing error

Break

Enable bits | UART interrupt requests |

THREINT

IER(ETBEI) ![]()

RDRINT

IER(ERBI)

RTOINT

RLSINT

IER(ELSI)

Arbiter

UART interrupt request to CPU

SPRU997C | Universal Asynchronous Receiver/Transmitter (UART) | 19 |

Submit Documentation Feedback |

|

|

Copyright © 2009, Texas Instruments Incorporated