www.ti.com

VLYNQ Port Registers

3VLYNQ Port Registers

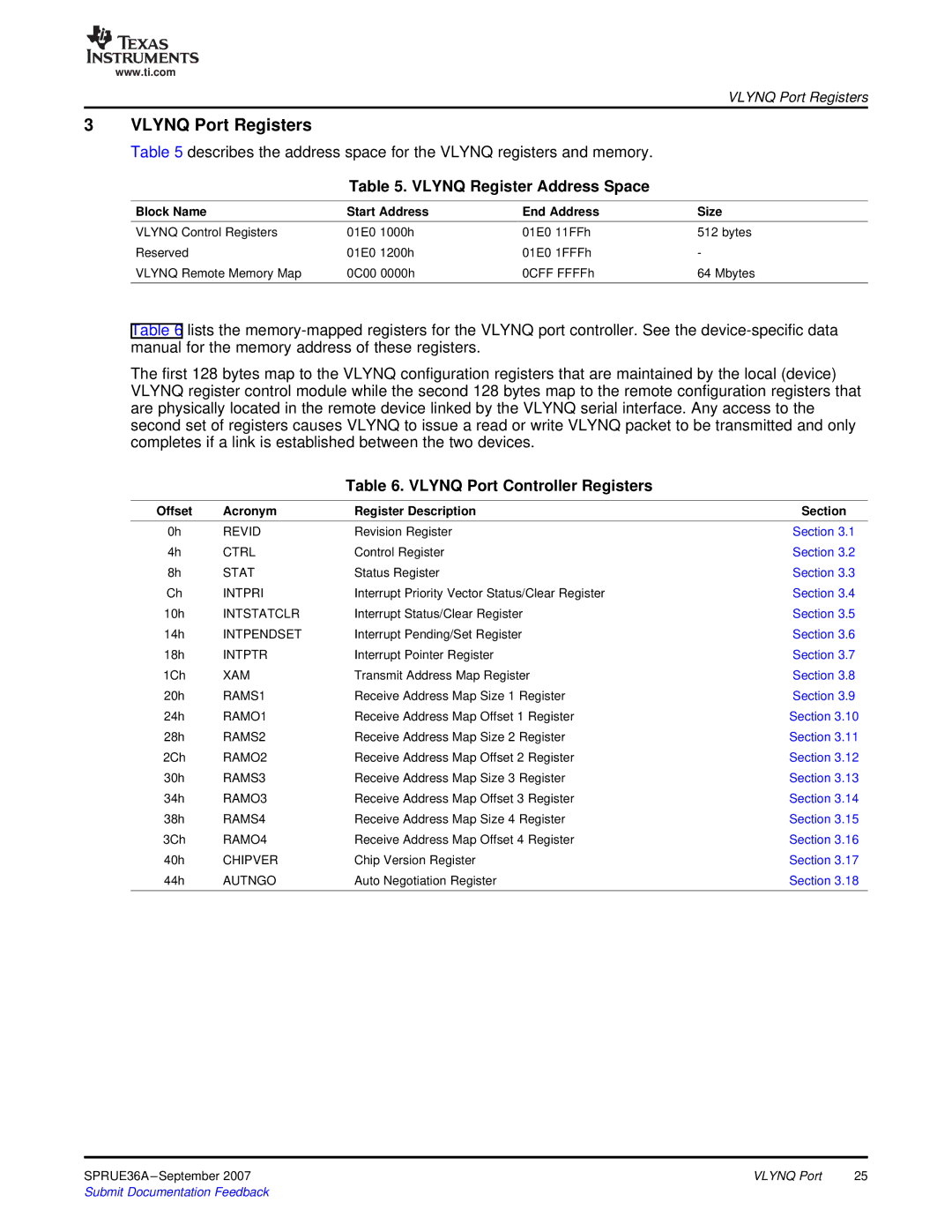

Table 5 describes the address space for the VLYNQ registers and memory.

Table 5. VLYNQ Register Address Space

Block Name | Start Address | End Address | Size |

VLYNQ Control Registers | 01E0 1000h | 01E0 11FFh | 512 bytes |

Reserved | 01E0 1200h | 01E0 1FFFh | - |

VLYNQ Remote Memory Map | 0C00 0000h | 0CFF FFFFh | 64 Mbytes |

Table 6 lists the

The first 128 bytes map to the VLYNQ configuration registers that are maintained by the local (device) VLYNQ register control module while the second 128 bytes map to the remote configuration registers that are physically located in the remote device linked by the VLYNQ serial interface. Any access to the second set of registers causes VLYNQ to issue a read or write VLYNQ packet to be transmitted and only completes if a link is established between the two devices.

Table 6. VLYNQ Port Controller Registers

Offset | Acronym | Register Description | Section |

0h | REVID | Revision Register | Section 3.1 |

4h | CTRL | Control Register | Section 3.2 |

8h | STAT | Status Register | Section 3.3 |

Ch | INTPRI | Interrupt Priority Vector Status/Clear Register | Section 3.4 |

10h | INTSTATCLR | Interrupt Status/Clear Register | Section 3.5 |

14h | INTPENDSET | Interrupt Pending/Set Register | Section 3.6 |

18h | INTPTR | Interrupt Pointer Register | Section 3.7 |

1Ch | XAM | Transmit Address Map Register | Section 3.8 |

20h | RAMS1 | Receive Address Map Size 1 Register | Section 3.9 |

24h | RAMO1 | Receive Address Map Offset 1 Register | Section 3.10 |

28h | RAMS2 | Receive Address Map Size 2 Register | Section 3.11 |

2Ch | RAMO2 | Receive Address Map Offset 2 Register | Section 3.12 |

30h | RAMS3 | Receive Address Map Size 3 Register | Section 3.13 |

34h | RAMO3 | Receive Address Map Offset 3 Register | Section 3.14 |

38h | RAMS4 | Receive Address Map Size 4 Register | Section 3.15 |

3Ch | RAMO4 | Receive Address Map Offset 4 Register | Section 3.16 |

40h | CHIPVER | Chip Version Register | Section 3.17 |

44h | AUTNGO | Auto Negotiation Register | Section 3.18 |

SPRUE36A | VLYNQ Port | 25 |

Submit Documentation Feedback |

|

|