www.ti.com

Peripheral Architecture

Note: Not servicing read operations results in deadlock. The only way to recover from a deadlock situation is to perform a hard reset. Read operations are typically not serviced due to read requests that are issued to a

Generally, you should not use read operations to transfer data packets since the serial nature of the interface could potentially result in longer latencies. See Appendix B for more information.

2.6Initialization

Since VLYNQ devices can be controlled solely over the serial interface (that is, no local CPU exists), an automatic reliable initialization sequence (without user configuration) establishes a connection between two VLYNQ devices, just after a VLYNQ module is enabled and

Bit 0 in the VLYNQ status register (LINK bit) is set to 1 when a link is established.

A link pulse timer generates a periodic link code every 2048 serial clock cycles. The link is lost when time expires and no link code has been detected during a period of 4096 serial clock cycles.

2.7Auto-Negotiation

The auto width negotiation does not occur until after completion of the VLYNQ 1.x legacy width configuration, which involves a period of 2000 VLYNQ 1.x system clock cycles for connection to VLYNQ 1.x devices. After the VLYNQ 1.x has determined its width, it receives the VLYNQ2.x auto width negotiation protocol. The VLYNQ 1.x device does not recognize this protocol and transmits error codes over the serial interface. The received error codes allow the VLYNQ 2.x devices to determine how many serial pins are valid on the connected VLYNQ 1.x device.

Once the width is established, VLYNQ further identifies the version (version 1.x or version 2.x ) of the remote VLYNQ. This better determines the capabilities of the connected VLYNQ device. This is software readable via the VLYNQ

2.8Serial Interface Width Configuration

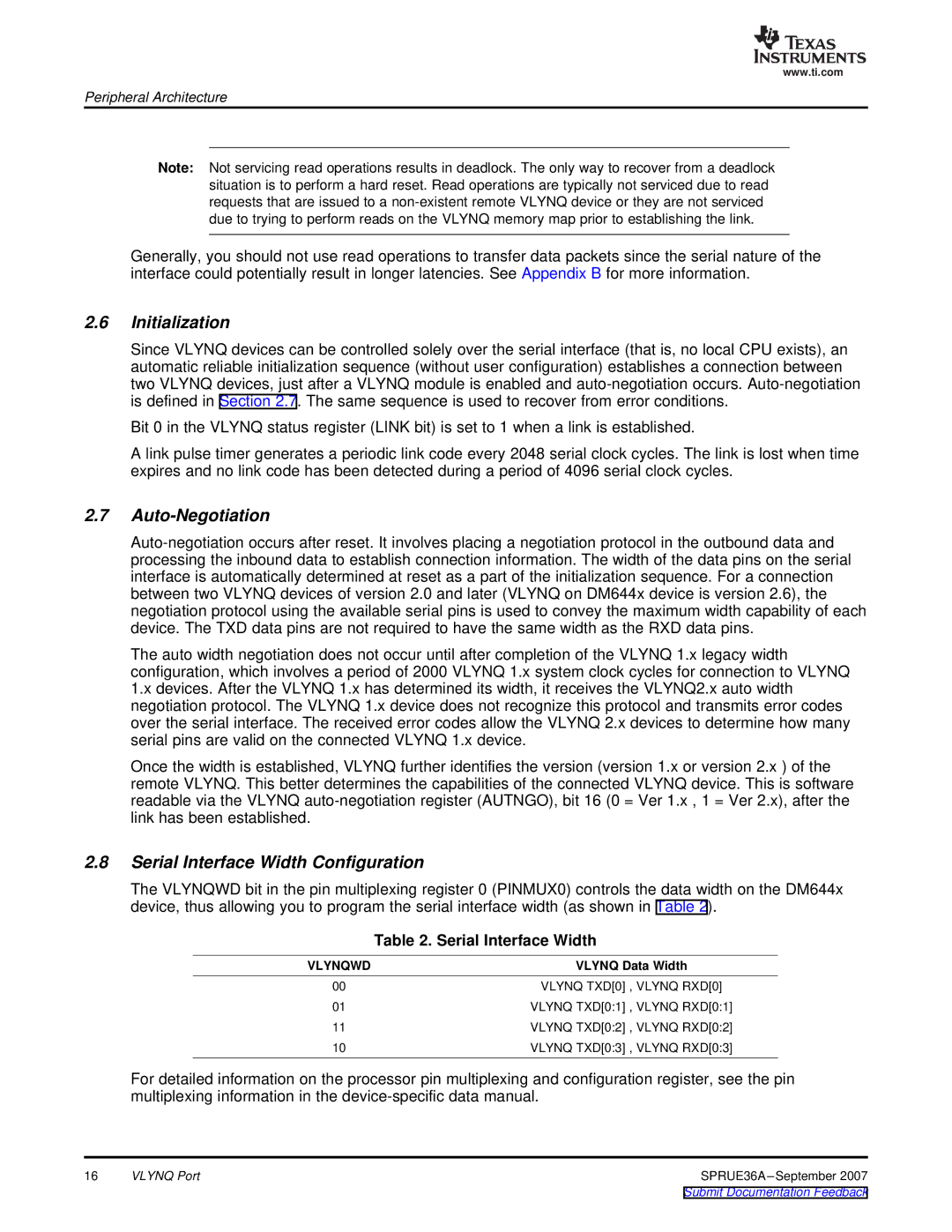

The VLYNQWD bit in the pin multiplexing register 0 (PINMUX0) controls the data width on the DM644x device, thus allowing you to program the serial interface width (as shown in Table 2).

| Table 2. Serial Interface Width |

VLYNQWD | VLYNQ Data Width |

00 | VLYNQ TXD[0] , VLYNQ RXD[0] |

01 | VLYNQ TXD[0:1] , VLYNQ RXD[0:1] |

11 | VLYNQ TXD[0:2] , VLYNQ RXD[0:2] |

10 | VLYNQ TXD[0:3] , VLYNQ RXD[0:3] |

For detailed information on the processor pin multiplexing and configuration register, see the pin multiplexing information in the

16 | VLYNQ Port | SPRUE36A |