www.ti.com

VLYNQ Port Registers

3.3Status Register (STAT)

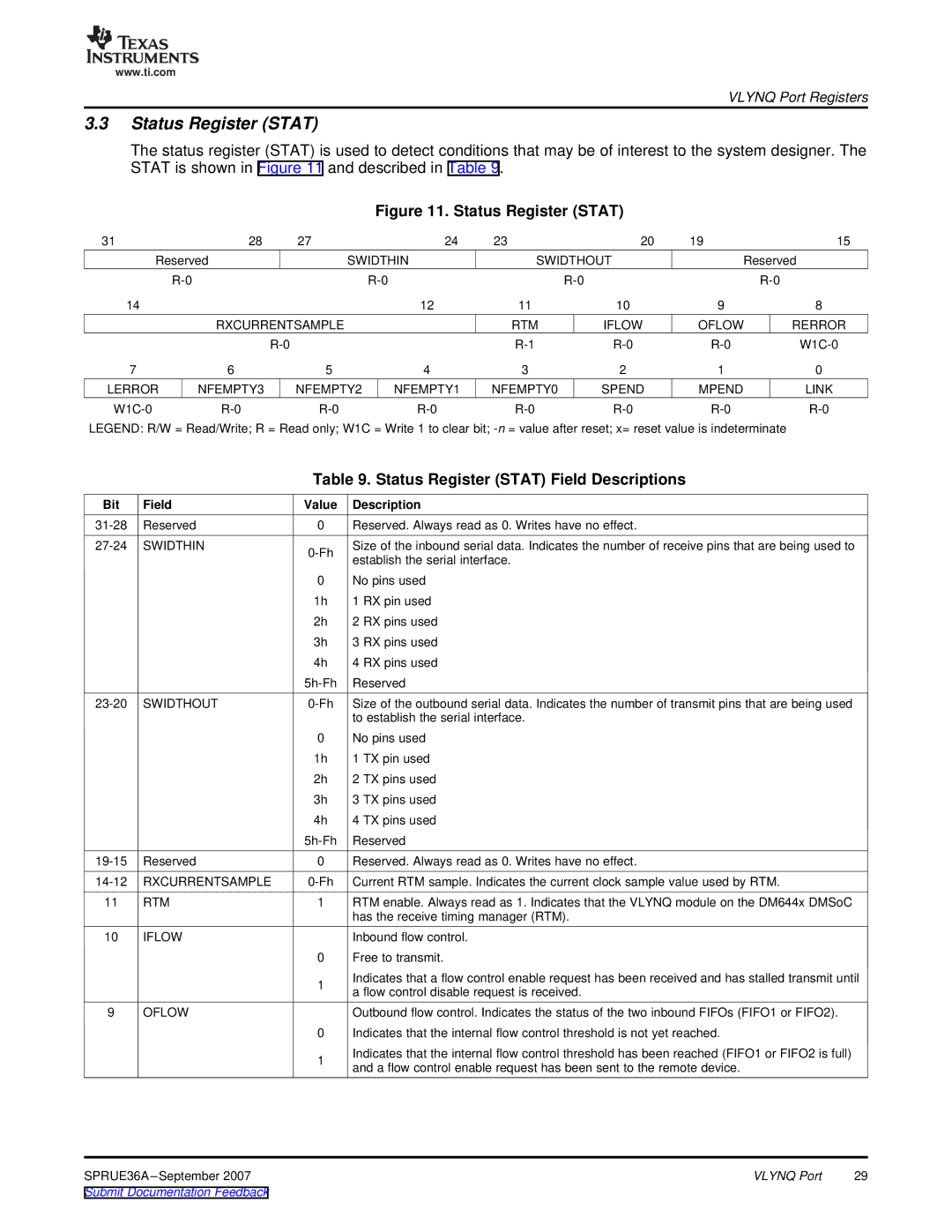

The status register (STAT) is used to detect conditions that may be of interest to the system designer. The STAT is shown in Figure 11 and described in Table 9.

Figure 11. Status Register (STAT)

31 | 28 | 27 | 24 | 23 | 20 | 19 | 15 |

Reserved | SWIDTHIN | SWIDTHOUT | Reserved | ||||

|

|

|

| ||||

14 |

|

| 12 | 11 | 10 | 9 | 8 |

| RXCURRENTSAMPLE |

| RTM | IFLOW | OFLOW | RERROR | |

|

|

| |||||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

LERROR | NFEMPTY3 | NFEMPTY2 | NFEMPTY1 | NFEMPTY0 | SPEND | MPEND | LINK |

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear bit;

Table 9. Status Register (STAT) Field Descriptions

Bit | Field | Value | Description | |

Reserved | 0 | Reserved. Always read as 0. Writes have no effect. | ||

SWIDTHIN | Size of the inbound serial data. Indicates the number of receive pins that are being used to | |||

|

| establish the serial interface. | ||

|

|

| ||

|

| 0 | No pins used | |

|

| 1h | 1 | RX pin used |

|

| 2h | 2 | RX pins used |

|

| 3h | 3 | RX pins used |

|

| 4h | 4 | RX pins used |

|

| Reserved | ||

SWIDTHOUT | Size of the outbound serial data. Indicates the number of transmit pins that are being used | |||

|

|

| to establish the serial interface. | |

|

| 0 | No pins used | |

|

| 1h | 1 | TX pin used |

|

| 2h | 2 | TX pins used |

|

| 3h | 3 | TX pins used |

|

| 4h | 4 | TX pins used |

|

| Reserved | ||

Reserved | 0 | Reserved. Always read as 0. Writes have no effect. | ||

RXCURRENTSAMPLE | Current RTM sample. Indicates the current clock sample value used by RTM. | |||

11 | RTM | 1 | RTM enable. Always read as 1. Indicates that the VLYNQ module on the DM644x DMSoC | |

|

|

| has the receive timing manager (RTM). | |

10 IFLOW

0

1

9 OFLOW

0

1

![]() Inbound flow control.

Inbound flow control.

Free to transmit.

Indicates that a flow control enable request has been received and has stalled transmit until a flow control disable request is received.

![]() Outbound flow control. Indicates the status of the two inbound FIFOs (FIFO1 or FIFO2). Indicates that the internal flow control threshold is not yet reached.

Outbound flow control. Indicates the status of the two inbound FIFOs (FIFO1 or FIFO2). Indicates that the internal flow control threshold is not yet reached.

Indicates that the internal flow control threshold has been reached (FIFO1 or FIFO2 is full) and a flow control enable request has been sent to the remote device.

SPRUE36A | VLYNQ Port | 29 |

Submit Documentation Feedback |

|

|