7-3-4. Color Signal Process Circuit

The color signal is level adjusted in the ACC (automatic color control) circuit, corrected in passing through a band pass circuit in the NTSC/PAL system, or a bell filter correction is carried out in the SECAM system, and then enters the color demodulation circuit.

The input burst signal is locked with a crystal oscillator frequency (3.58 MHz/4.43 MHz) in the PLL circuit and then demodulated into color difference signals after a tint adjustment (in the NTSC system). The demodulation for the SECAM signal is carried out using a PLL circuit.

The demodulated color difference signals are output through low pass filters, delayed by 1H in passing through TDA4665T, fed to TDA9141 again and directly output.

7-3-5. Picture Sharpness Correction Circuit

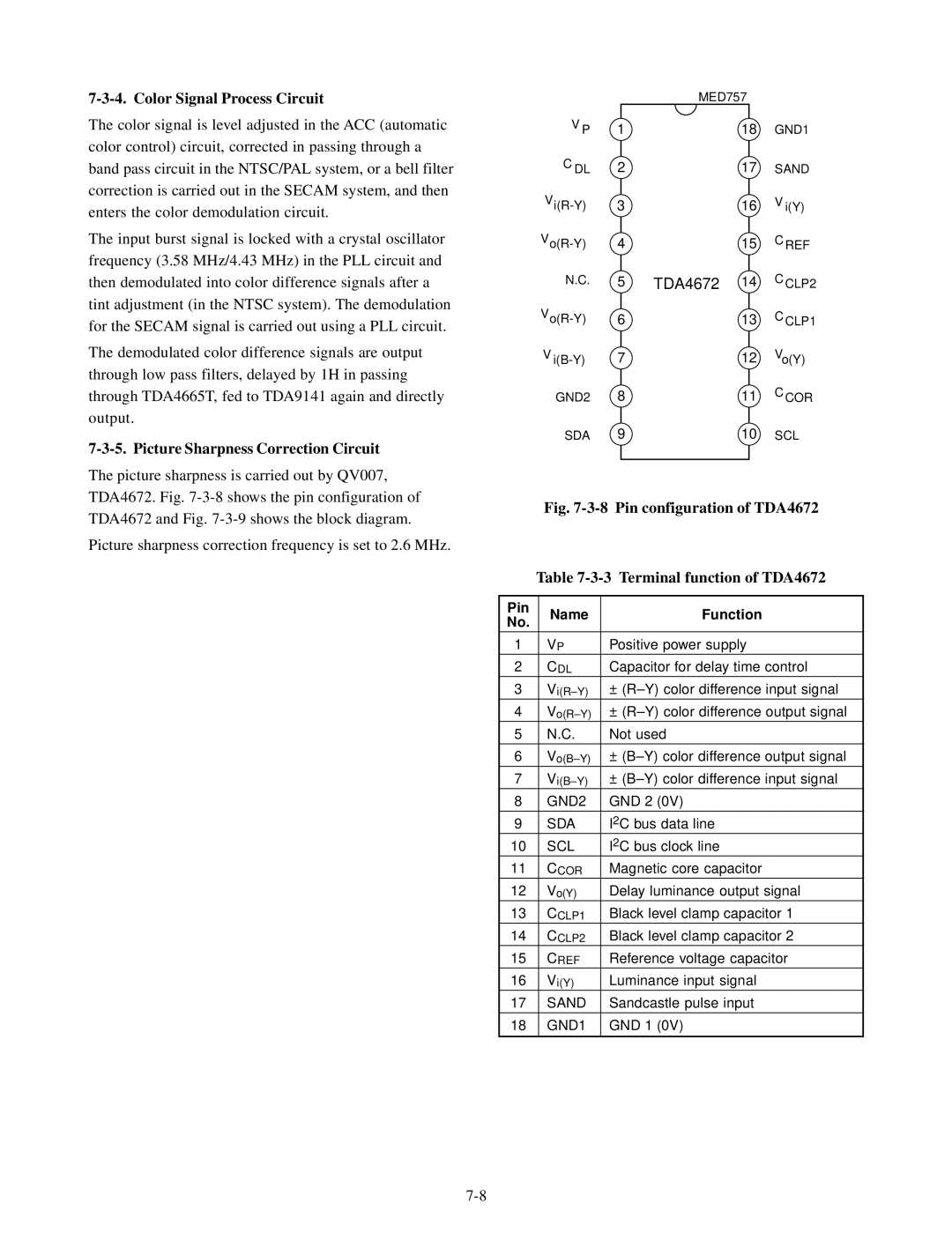

The picture sharpness is carried out by QV007, TDA4672. Fig.

Picture sharpness correction frequency is set to 2.6 MHz.

|

| MED757 |

|

V P | 1 | 18 | GND1 |

C DL | 2 | 17 | SAND |

3 | 16 | V i(Y) | |

4 | 15 | C REF | |

N.C. | 5 | TDA4672 14 | C CLP2 |

6 | 13 | C CLP1 | |

V | 7 | 12 | Vo(Y) |

GND2 | 8 | 11 | C COR |

SDA | 9 | 10 | SCL |

Fig. 7-3-8 Pin configuration of TDA4672

Table 7-3-3 Terminal function of TDA4672

Pin | Name | Function | |

No. | |||

|

| ||

1 | VP | Positive power supply | |

2 | CDL | Capacitor for delay time control | |

3 | ± | ||

4 | ± | ||

5 | N.C. | Not used | |

6 | ± | ||

7 | ± | ||

8 | GND2 | GND 2 (0V) | |

9 | SDA | I2C bus data line | |

10 | SCL | I2C bus clock line | |

11 | CCOR | Magnetic core capacitor | |

12 | Vo(Y) | Delay luminance output signal | |

13 | CCLP1 | Black level clamp capacitor 1 | |

14 | CCLP2 | Black level clamp capacitor 2 | |

15 | CREF | Reference voltage capacitor | |

16 | Vi(Y) | Luminance input signal | |

17 | SAND | Sandcastle pulse input | |

18 | GND1 | GND 1 (0V) | |

|

|

|