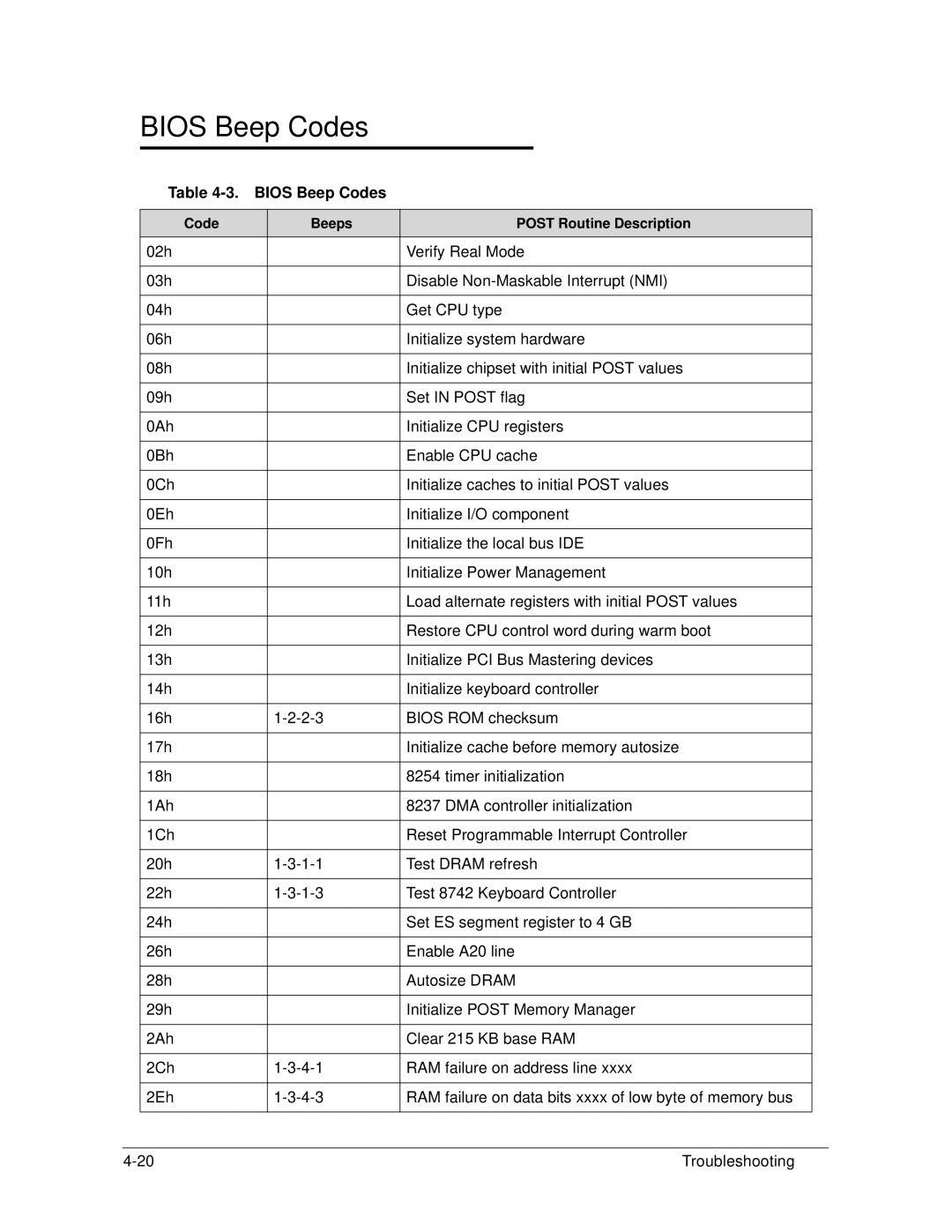

BIOS Beep Codes

Table 4-3. BIOS Beep Codes

Code | Beeps | POST Routine Description |

02h |

| Verify Real Mode |

|

|

|

03h |

| Disable |

|

|

|

04h |

| Get CPU type |

|

|

|

06h |

| Initialize system hardware |

|

|

|

08h |

| Initialize chipset with initial POST values |

|

|

|

09h |

| Set IN POST flag |

|

|

|

0Ah |

| Initialize CPU registers |

|

|

|

0Bh |

| Enable CPU cache |

|

|

|

0Ch |

| Initialize caches to initial POST values |

|

|

|

0Eh |

| Initialize I/O component |

|

|

|

0Fh |

| Initialize the local bus IDE |

|

|

|

10h |

| Initialize Power Management |

|

|

|

11h |

| Load alternate registers with initial POST values |

|

|

|

12h |

| Restore CPU control word during warm boot |

|

|

|

13h |

| Initialize PCI Bus Mastering devices |

|

|

|

14h |

| Initialize keyboard controller |

|

|

|

16h | BIOS ROM checksum | |

|

|

|

17h |

| Initialize cache before memory autosize |

|

|

|

18h |

| 8254 timer initialization |

|

|

|

1Ah |

| 8237 DMA controller initialization |

|

|

|

1Ch |

| Reset Programmable Interrupt Controller |

|

|

|

20h | Test DRAM refresh | |

|

|

|

22h | Test 8742 Keyboard Controller | |

|

|

|

24h |

| Set ES segment register to 4 GB |

|

|

|

26h |

| Enable A20 line |

|

|

|

28h |

| Autosize DRAM |

|

|

|

29h |

| Initialize POST Memory Manager |

|

|

|

2Ah |

| Clear 215 KB base RAM |

|

|

|

2Ch | RAM failure on address line xxxx | |

|

|

|

2Eh | RAM failure on data bits xxxx of low byte of memory bus | |

|

|

|

Troubleshooting |