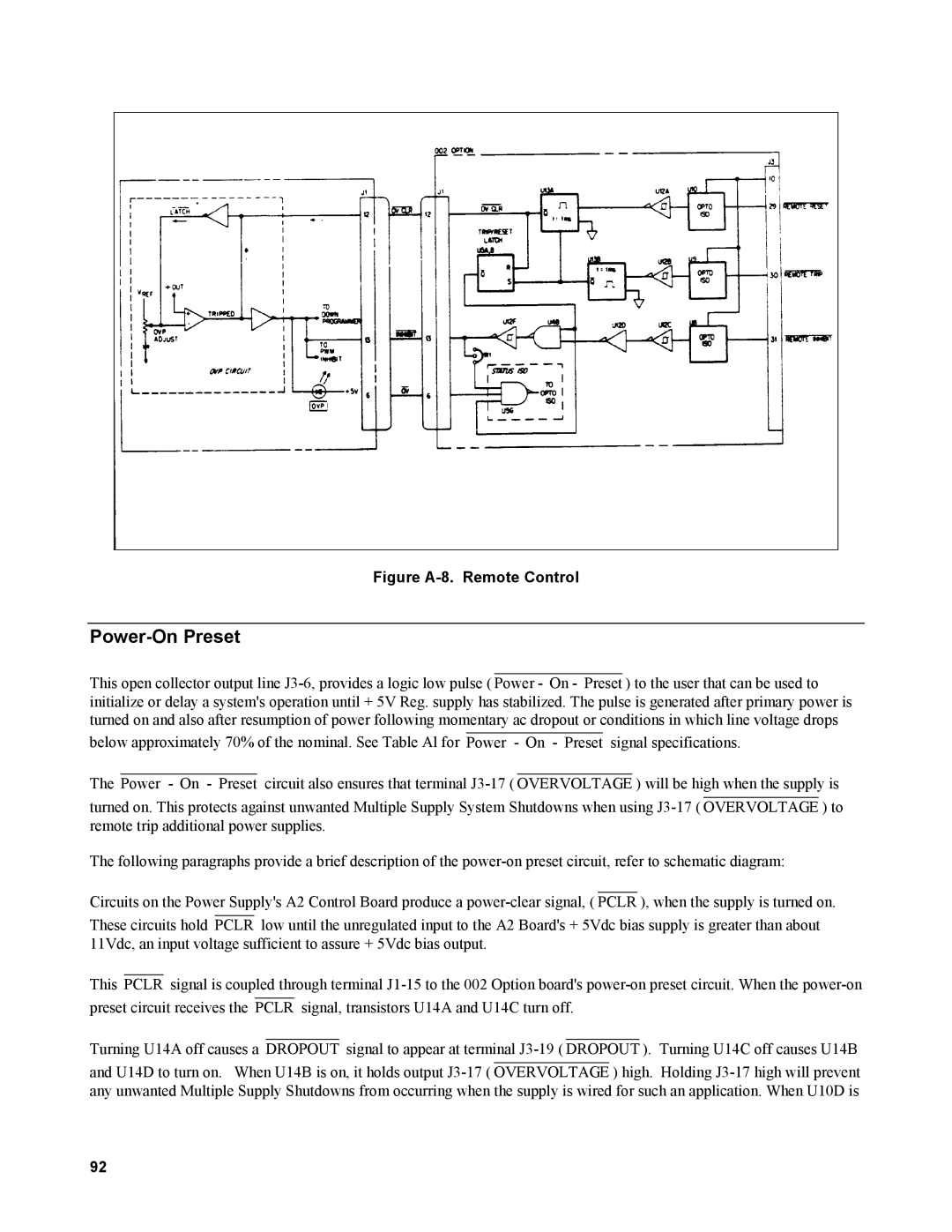

Figure A-8. Remote Control

Power-On Preset

This open collector output line

below approximately 70% of the nominal. See Table Al for Power - On - Preset signal specifications.

The Power - On - Preset circuit also ensures that terminal

turned on. This protects against unwanted Multiple Supply System Shutdowns when using

The following paragraphs provide a brief description of the

Circuits on the Power Supply's A2 Control Board produce a

These circuits hold PCLR low until the unregulated input to the A2 Board's + 5Vdc bias supply is greater than about 11Vdc, an input voltage sufficient to assure + 5Vdc bias output.

This PCLR signal is coupled through terminal

preset circuit receives the PCLR signal, transistors U14A and U14C turn off.

Turning U14A off causes a DROPOUT signal to appear at terminal

and U14D to turn on. When U14B is on, it holds output

92