a

DSP Microcomputers

ADSP-2181/ADSP-2183

FEATURES PERFORMANCE

30 ns Instruction Cycle Time @ 5.0 Volts

33 MIPS Sustained Performance

34.7ns Instruction Cycle Time @ 3.3 Volts

Multifunction Instructions

Low Power Dissipation in Idle Mode

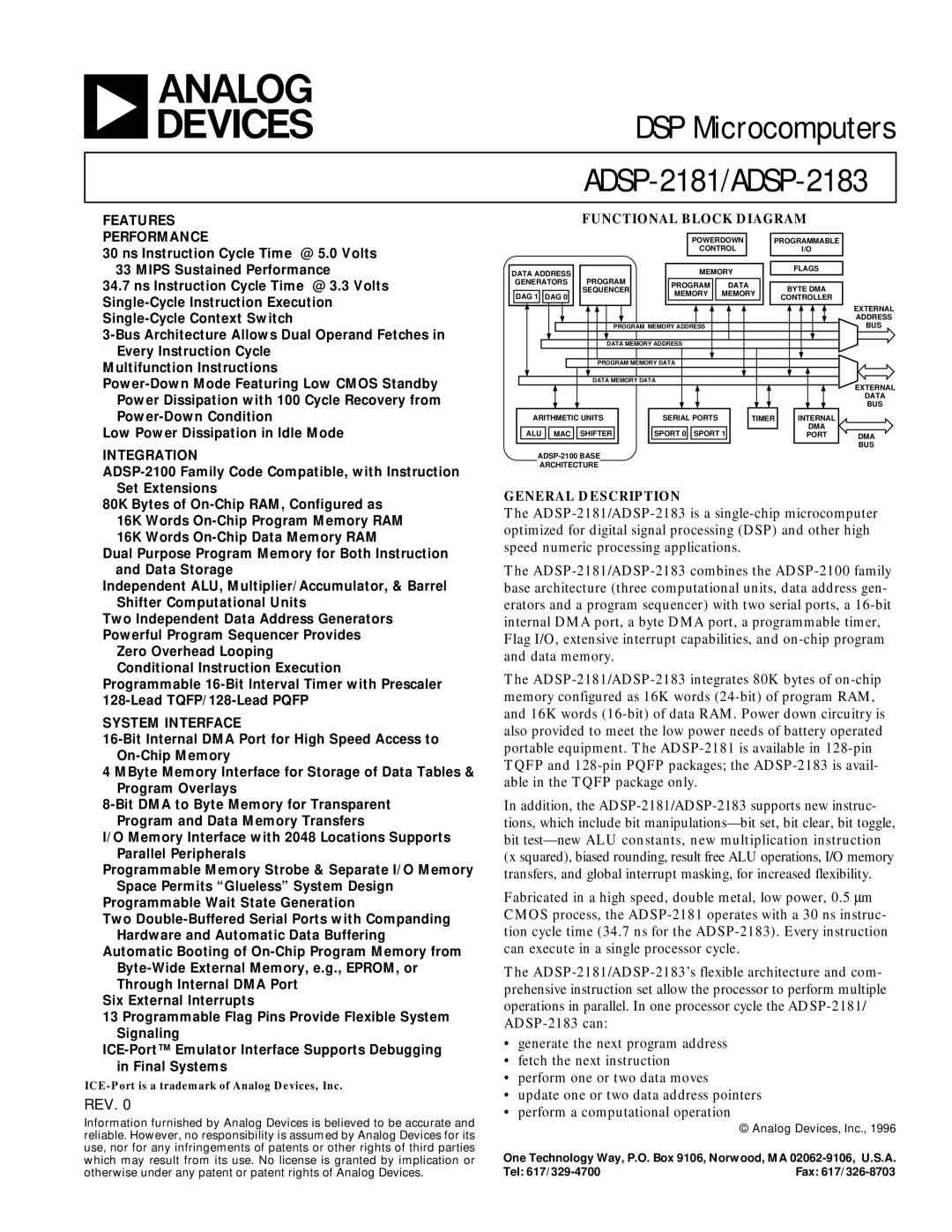

| FUNCTIONAL BLOCK DIAGRAM | ||||

|

| POWERDOWN | PROGRAMMABLE | ||

|

| CONTROL | I/O | ||

DATA ADDRESS |

| MEMORY | FLAGS | ||

PROGRAM |

| ||||

GENERATORS | PROGRAM | DATA | BYTE DMA | ||

| SEQUENCER | ||||

DAG 1 DAG 0 | MEMORY | MEMORY | |||

| CONTROLLER | ||||

|

|

| |||

|

|

|

| EXTERNAL | |

|

|

|

| ADDRESS | |

| PROGRAM MEMORY ADDRESS |

| BUS | ||

DATA MEMORY ADDRESS

|

| PROGRAM MEMORY DATA |

|

|

|

| |

|

| DATA MEMORY DATA |

|

|

| EXTERNAL | |

|

|

|

|

|

|

| |

|

|

|

|

|

|

| DATA |

|

|

|

|

|

|

| BUS |

ARITHMETIC UNITS | SERIAL PORTS | TIMER | INTERNAL |

| |||

ALU | MAC | SHIFTER | SPORT 0 | SPORT 1 |

| DMA |

|

| PORT | DMA | |||||

|

|

|

|

|

|

| BUS |

INTEGRATION

80K Bytes of

16K Words

16K Words

Dual Purpose Program Memory for Both Instruction and Data Storage

Independent ALU, Multiplier/Accumulator, & Barrel Shifter Computational Units

Two Independent Data Address Generators Powerful Program Sequencer Provides

Zero Overhead Looping Conditional Instruction Execution

Programmable

SYSTEM INTERFACE

4 MByte Memory Interface for Storage of Data Tables & Program Overlays

I/O Memory Interface with 2048 Locations Supports Parallel Peripherals

Programmable Memory Strobe & Separate I/O Memory Space Permits “Glueless” System Design

Programmable Wait State Generation

Two

Automatic Booting of

Six External Interrupts

13 Programmable Flag Pins Provide Flexible System Signaling

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

ARCHITECTURE

GENERAL DESCRIPTION

The

The

The

In addition, the

Fabricated in a high speed, double metal, low power, 0.5 μm CMOS process, the

The

•generate the next program address

•fetch the next instruction

•perform one or two data moves

•update one or two data address pointers

•perform a computational operation

© Analog Devices, Inc., 1996

One Technology Way, P.O. Box 9106, Norwood, MA

Tel: | Fax: |