ADSP-2181/ADSP-2183

When the BWCOUNT register is written with a nonzero value the BDMA circuit starts executing byte memory accesses with wait states set by BMWAIT. These accesses continue until the count reaches zero. When enough accesses have occurred to create a destination word, it is transferred to or from

The BDMA Context Reset bit (BCR) controls whether the processor is held off while the BDMA accesses are occurring. Setting the BCR bit to 0 allows the processor to continue opera- tions. Setting the BCR bit to 1 causes the processor to stop ex- ecution while the BDMA accesses are occurring, to clear the context of the processor, and start execution at address 0 when the BDMA accesses have completed.

Internal Memory DMA Port (IDMA Port)

The IDMA Port provides an efficient means of communication between a host system and the

The IDMA port has a

The DSP memory address is latched and then is automatically incremented after each IDMA transaction. An external device can therefore access a block of sequentially addressed memory by specifying only the starting address of the block. This in- creases throughput as the address does not have to be sent for each memory access.

IDMA Port access occurs in two phases. The first is the IDMA Address Latch cycle. When the acknowledge is asserted, a 14- bit address and

Once the address is stored, data can then be either read from, or written to, the

Once an access has occurred, the latched address is automati- cally incremented, and another access can occur.

Through the IDMAA register, the DSP can also specify the starting address and data format for DMA operation.

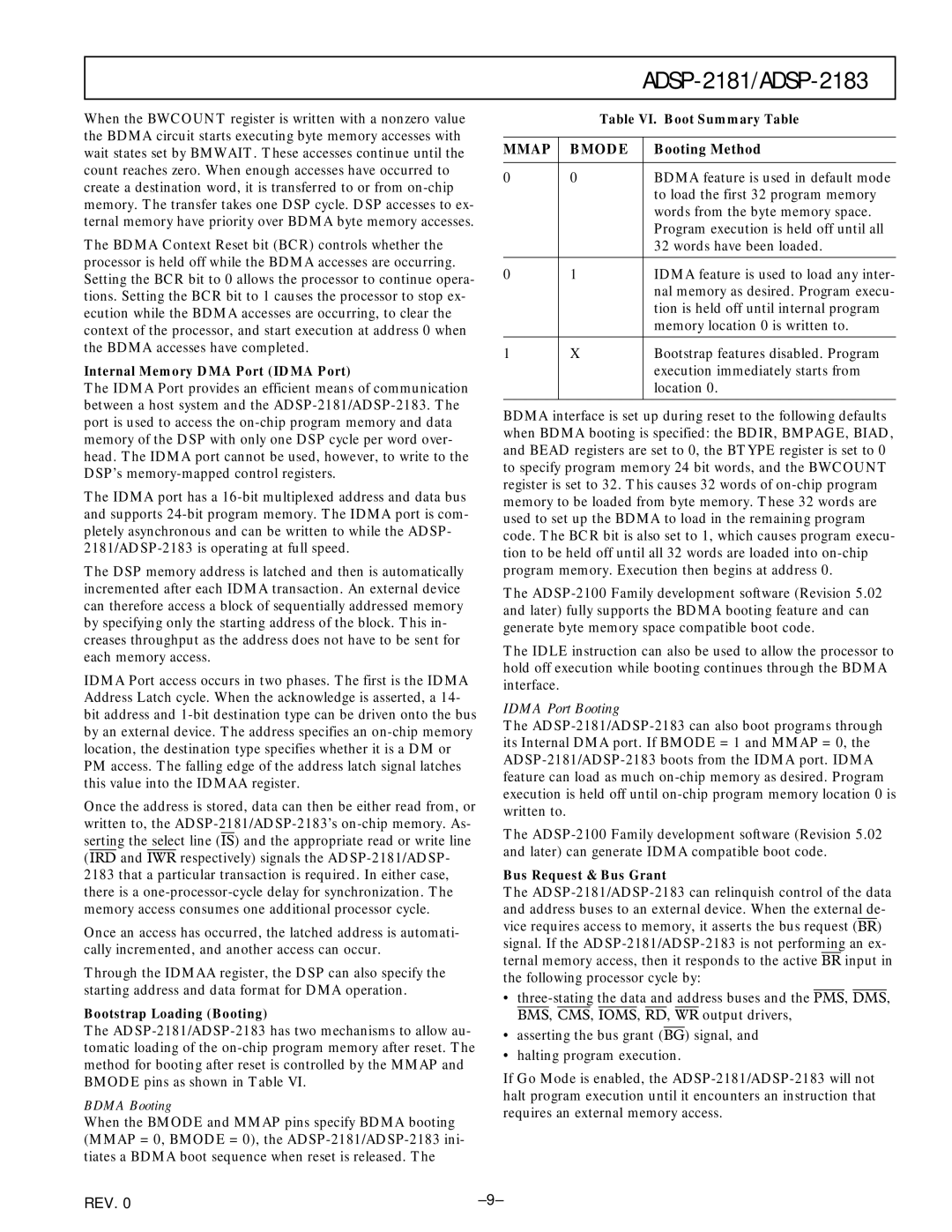

Table VI. Boot Summary Table

MMAP | BMODE | Booting Method |

|

|

|

0 | 0 | BDMA feature is used in default mode |

|

| to load the first 32 program memory |

|

| words from the byte memory space. |

|

| Program execution is held off until all |

|

| 32 words have been loaded. |

|

|

|

0 | 1 | IDMA feature is used to load any inter- |

|

| nal memory as desired. Program execu- |

|

| tion is held off until internal program |

|

| memory location 0 is written to. |

|

|

|

1 | X | Bootstrap features disabled. Program |

|

| execution immediately starts from |

|

| location 0. |

|

|

|

BDMA interface is set up during reset to the following defaults when BDMA booting is specified: the BDIR, BMPAGE, BIAD, and BEAD registers are set to 0, the BTYPE register is set to 0 to specify program memory 24 bit words, and the BWCOUNT register is set to 32. This causes 32 words of

The

The IDLE instruction can also be used to allow the processor to hold off execution while booting continues through the BDMA interface.

IDMA Port Booting

The

The

Bus Request & Bus Grant

The

•

Bootstrap Loading (Booting)

The

BDMA Booting

When the BMODE and MMAP pins specify BDMA booting (MMAP = 0, BMODE = 0), the

REV. 0

BMS, CMS, IOMS, RD, WR output drivers,

•asserting the bus grant (BG) signal, and

•halting program execution.

If Go Mode is enabled, the