ADSP-2181/ADSP-2183

ADSP-2181

Parameter |

|

| Min | Max | Unit |

|

|

|

|

| |

Clock Signals and Reset |

|

|

| ||

Timing Requirements: |

|

|

| ||

tCKI | CLKIN Period | 60 | 150 | ns | |

tCKIL | CLKIN Width Low | 20 |

| ns | |

tCKIH | CLKIN Width High | 20 |

| ns | |

Switching Characteristics: |

|

|

| ||

tCKL | CLKOUT Width Low | 0.5tCK – 7 |

| ns | |

tCKH | CLKOUT Width High | 0.5tCK – 7 |

| ns | |

tCKOH | CLKIN High to CLKOUT High | 0 | 20 | ns | |

Control Signals |

|

|

|

|

|

Timing Requirements: | 5tCK1 |

|

| ||

tRSP | RESET | Width Low |

| ns | |

ADSP-2183

|

|

| 28.8 MHz |

|

Parameter |

|

| Min | Max |

Clock Signals and Reset |

|

| ||

Timing Requirements: |

|

| ||

tCKI | CLKIN Period | 69.4 | 150 | |

tCKIL | CLKIN Width Low | 20 |

| |

tCKIH | CLKIN Width High | 20 |

| |

Switching Characteristics: |

|

| ||

tCKL | CLKOUT Width Low | 0.5tCK – 7 |

| |

tCKH | CLKOUT Width High | 0.5tCK – 7 |

| |

tCKOH | CLKIN High to CLKOUT High | 0 | 20 | |

Control Signals |

|

|

|

|

Timing Requirements: | 5tCK1 |

| ||

tRSP | RESET | Width Low |

| |

NOTE

Unit

ns ns ns

ns ns ns

ns

1Applies after

oscillator

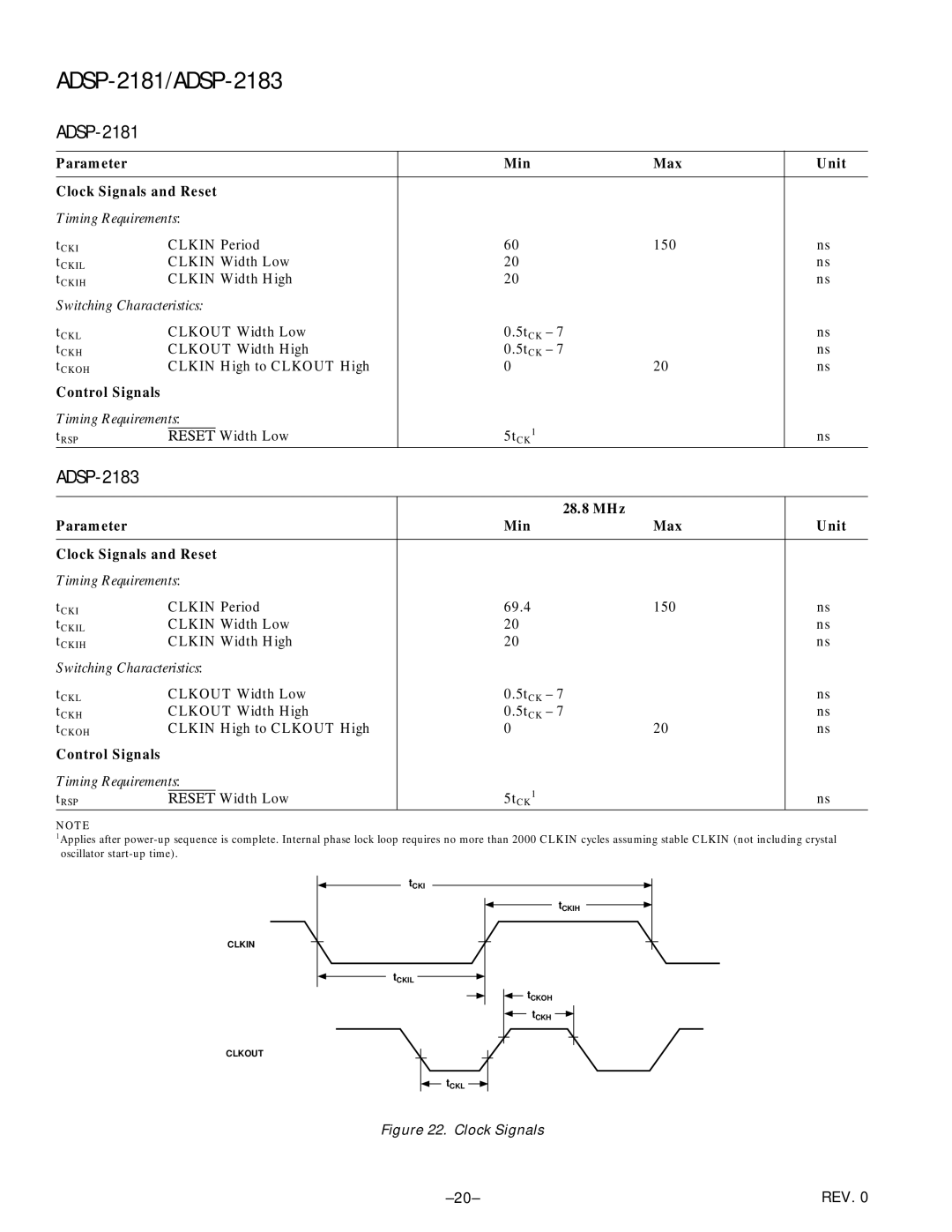

CLKIN

tCKI

tCKIL

tCKIH

tCKOH

tCKH

CLKOUT

tCKL ![]()

Figure 22. Clock Signals

REV. 0 |