ADSP-2181/ADSP-2183

ADSP-2181

Parameter |

|

| Min | Max | Unit |

|

|

|

|

| |

Interrupts and Flag |

|

|

| ||

Timing Requirements: |

|

|

| ||

tIFS |

| , FI, or PFx Setup before CLKOUT Low1, 2, 3, 4 | 0.25tCK + 15 |

| ns |

IRQx |

| ||||

tIFH | IRQx | , FI, or PFx Hold after CLKOUT High1, 2, 3, 4 | 0.25tCK |

| ns |

Switching Characteristics: |

|

|

| ||

tFOH | Flag Output Hold after CLKOUT Low5 | 0.5tCK – 7 |

| ns | |

tFOD | Flag Output Delay from CLKOUT Low5 |

| 0.25tCK + 5 | ns | |

ADSP-2183

|

|

| 28.8 MHz |

|

|

Parameter |

|

| Min | Max | Unit |

|

|

|

|

| |

Interrupts and Flag |

|

|

| ||

Timing Requirements: |

|

|

| ||

tIFS |

| , FI, or PFx Setup before CLKOUT Low1, 2, 3, 4 | 0.25tCK + 15 |

| ns |

IRQx |

| ||||

tIFH | IRQx | , FI, or PFx Hold after CLKOUT High1, 2, 3, 4 | 0.25tCK |

| ns |

Switching Characteristics: |

|

|

| ||

tFOH | Flag Output Hold after CLKOUT Low5 | 0.5tCK – 7 |

| ns | |

tFOD | Flag Output Delay from CLKOUT Low5 |

| 0.25tCK + 6 | ns | |

NOTES

1If IRQx and FI inputs meet tIFS and tIFH setup/hold requirements, they will be recognized during the current clock cycle; otherwise the signals will be recognized on the following cycle. (Refer to “Interrupt Controller Operation” in the Program Control chapter of the User’s Manual for further information on interrupt servicing.)

3IRQx = IRQ0, IRQ1, IRQ2, IRQL0, IRQL1, IRQE. 4PFx = PF0, PF1, PF2, PF3, PF4, PF5, PF6, PF7.

5Flag outputs = PFx, FL0, FL1, FL2, Flag_out4.

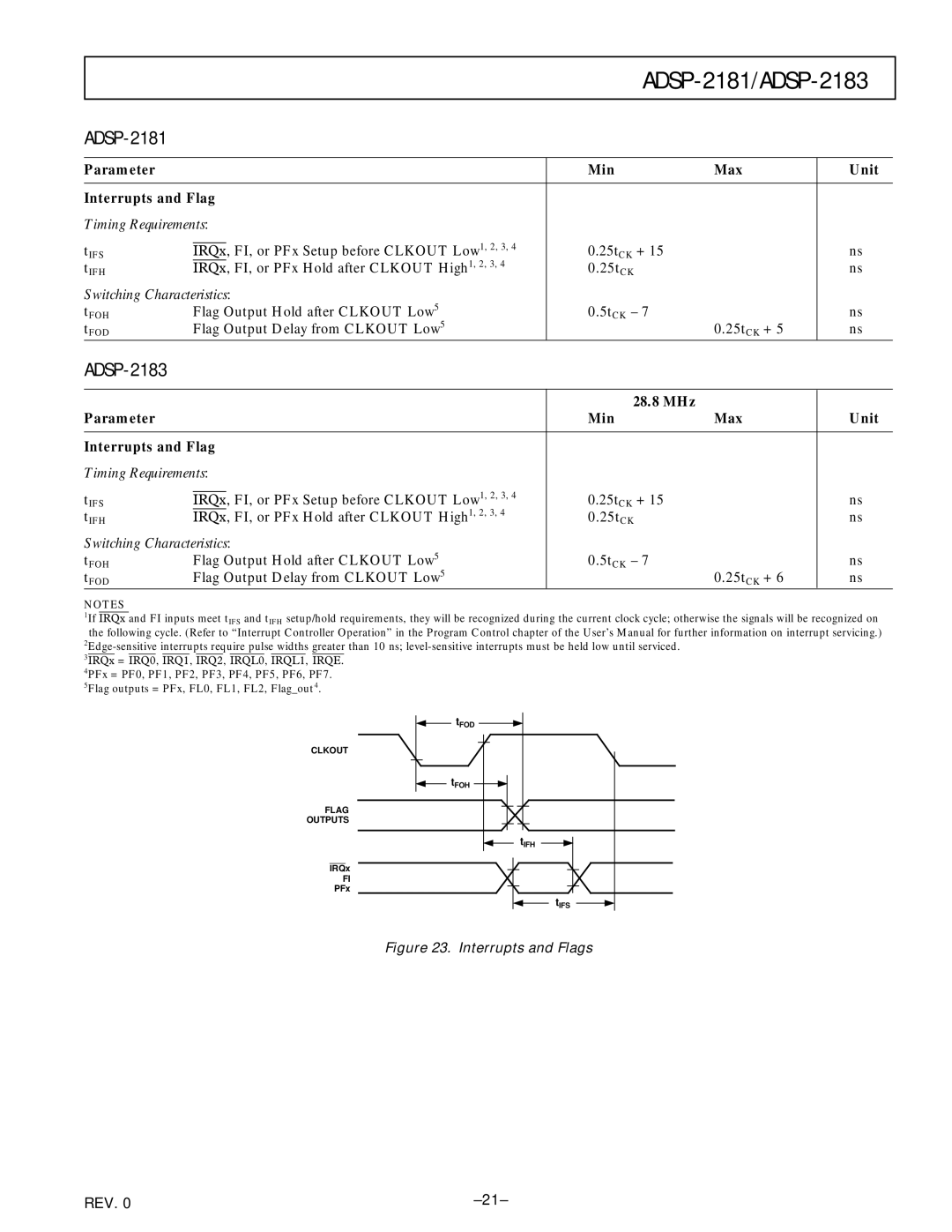

CLKOUT

FLAG

OUTPUTS

IRQx

FI

PFx

tFOD

tFOH |

tIFH |

tIFS |

Figure 23. Interrupts and Flags

REV. 0 |