Contents

Functional Block Diagram

General Description

ADSP-2181/ADSP-2183

Architecture Overview

ADSP-2181/ADSP-2183 Integration

Pin Input Names Pins Output Function

PIN Descriptions

Interrupt Vector

Source of Interrupt Address Hex

Highest Priority

Lowest Priority

System Interface

ADSP-2181 ADSP-2183

Pmovlay

Memory A13 A120

Address Range Wait State Register

Internal

Memory Space Word Size Alignment

Booting Method

Idma Port Booting

Syntax IOaddr = dreg dreg = IOaddr

Biased Rounding

Instruction SET Description

Designing AN EZ-ICE-COMPATIBLE System

Reset GND

PM, DM, BM, IOM, & CM

Grade Parameter Min Max Unit

Grades Parameter Test Conditions Min Max Unit

Memory Timing Specifications

Frequency Dependency for Timing Specifications

Absolute Maximum Ratings

ESD Sensitivity

Package

50C/W 2C/W 48C/W

41C/W 10C/W 31C/W

Capacitive Loading

Test Conditions

ADSP-2183-SPECIFICATIONS

ADSP-2183 Timing Parameters

Tqfp

Delay Valid Output

Parameter Min Max Unit Clock Signals and Reset

Control Signals

28.8 MHz Parameter Min Max Clock Signals and Reset

FI, or PFx Setup before Clkout Low1, 2, 3 25tCK + IRQx

Flag Output Delay from Clkout Low5 25tCK +

Parameter Min Max Unit Interrupts and Flag

Flag Output Hold after Clkout Low5 5tCK

Parameter Min Max Unit Bus Request/Grant

Parameter Min Max Unit Memory Read

28.8 MHz Parameter Min Max Unit Memory Read

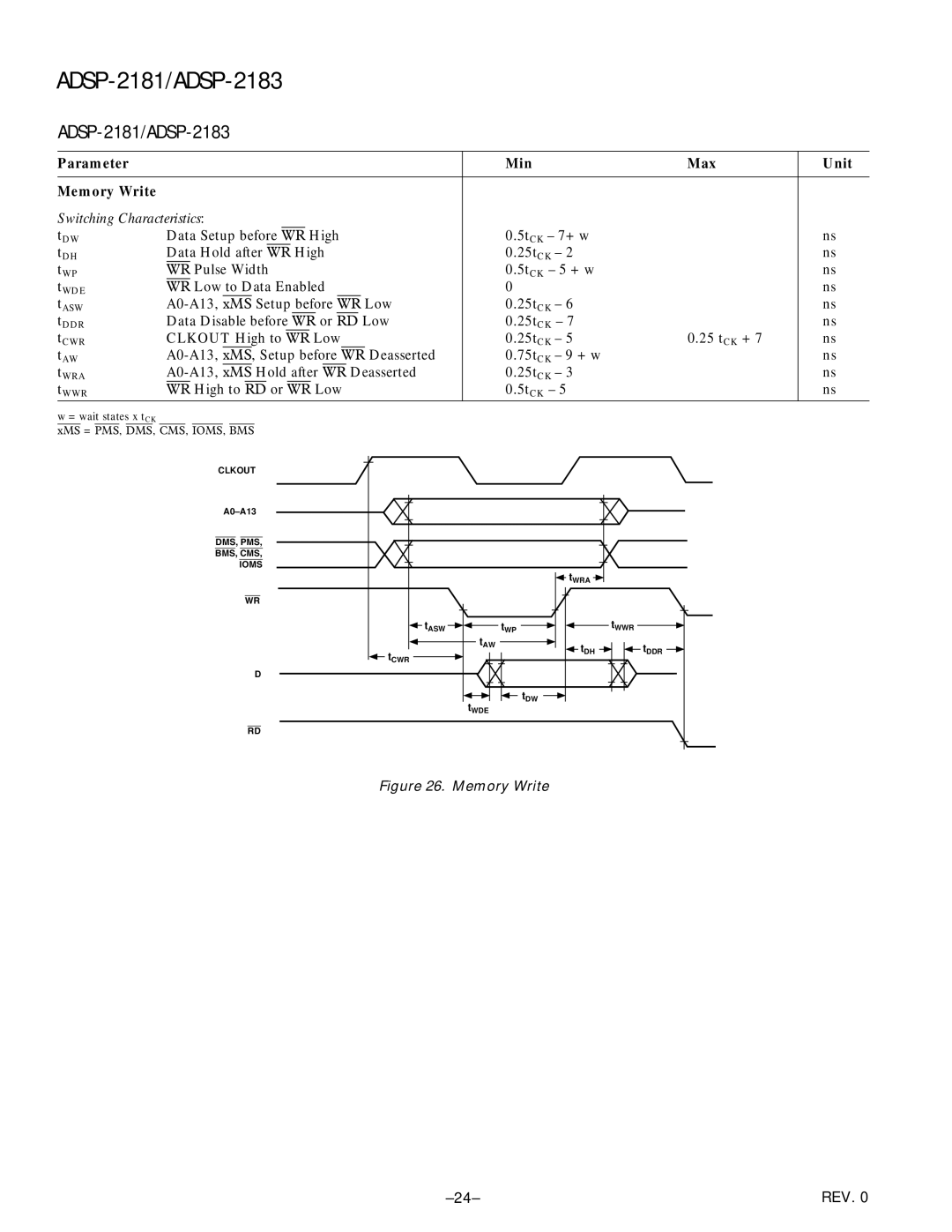

Parameter Min Max Unit Memory Write

Parameter Min Max Unit Serial Ports

Parameter Min Max Unit Idma Address Latch

Parameter Min Max Unit Idma Write, Short Write Cycle

28.8 MHz

Parameter Min Max Idma Write, Short Write Cycle

Parameter Min Max Unit Idma Write, Long Write Cycle

Parameter Min Max Unit Idma Read, Long Read Cycle

28.8 MHz Parameter Min Max Unit Idma Read, Long Read Cycle

Parameter Min Max Unit Idma Read, Short Read Cycle

28.8 MHz Parameter Min Max Unit Idma Read, Short Read Cycle

Lead Tqfp Package Pinout

Pin

Number Name

Millimeters Inches Symbol MIN TYP MAX

Outline Dimensions

Lead Pqfp Package Pinout

PF0

160

Ordering Guide

Page

Page

C2144-16-6/96

![]()

![]()

![]() tDW tWDE

tDW tWDE