Chapter 4 Configuring Interfaces

Configuring the POS

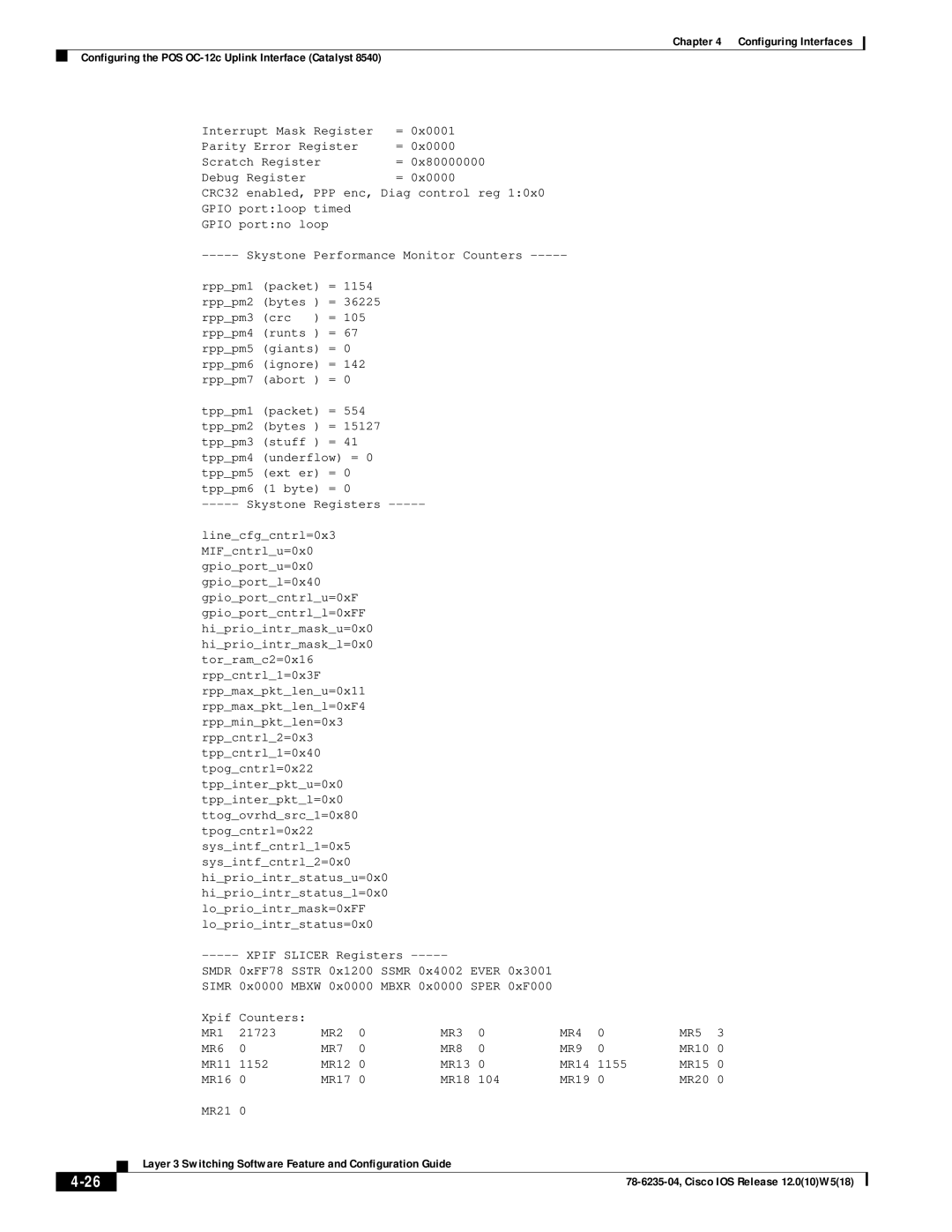

Interrupt Mask | Register | = 0x0001 |

Parity Error Register | = 0x0000 | |

Scratch Register | = 0x80000000 | |

Debug Register |

| = 0x0000 |

CRC32 enabled, | PPP enc, Diag control reg 1:0x0 | |

GPIO port:loop | timed |

|

GPIO port:no loop |

| |

Performance Monitor Counters | ||

rpp_pm1 (packet) = 1154 rpp_pm2 (bytes ) = 36225 rpp_pm3 (crc ) = 105 rpp_pm4 (runts ) = 67 rpp_pm5 (giants) = 0 rpp_pm6 (ignore) = 142 rpp_pm7 (abort ) = 0

tpp_pm1 (packet) = 554 tpp_pm2 (bytes ) = 15127 tpp_pm3 (stuff ) = 41 tpp_pm4 (underflow) = 0 tpp_pm5 (ext er) = 0 tpp_pm6 (1 byte) = 0

----- Skystone Registers -----

line_cfg_cntrl=0x3 MIF_cntrl_u=0x0 gpio_port_u=0x0 gpio_port_l=0x40 gpio_port_cntrl_u=0xF gpio_port_cntrl_l=0xFF hi_prio_intr_mask_u=0x0 hi_prio_intr_mask_l=0x0 tor_ram_c2=0x16 rpp_cntrl_1=0x3F rpp_max_pkt_len_u=0x11 rpp_max_pkt_len_l=0xF4 rpp_min_pkt_len=0x3 rpp_cntrl_2=0x3 tpp_cntrl_1=0x40 tpog_cntrl=0x22 tpp_inter_pkt_u=0x0 tpp_inter_pkt_l=0x0 ttog_ovrhd_src_1=0x80 tpog_cntrl=0x22 sys_intf_cntrl_1=0x5 sys_intf_cntrl_2=0x0 hi_prio_intr_status_u=0x0 hi_prio_intr_status_l=0x0 lo_prio_intr_mask=0xFF lo_prio_intr_status=0x0

|

|

|

|

|

|

|

| |||||

|

|

| SMDR | 0xFF78 SSTR 0x1200 SSMR 0x4002 EVER 0x3001 |

|

|

|

| ||||

|

|

| SIMR | 0x0000 MBXW 0x0000 MBXR 0x0000 SPER 0xF000 |

|

|

|

| ||||

|

|

| Xpif | Counters: |

|

|

|

|

|

|

|

|

|

|

| MR1 | 21723 | MR2 | 0 | MR3 | 0 | MR4 | 0 | MR5 3 | |

|

|

| MR6 | 0 | MR7 | 0 | MR8 | 0 | MR9 | 0 | MR10 0 | |

|

|

| MR11 | 1152 | MR12 0 | MR13 | 0 | MR14 | 1155 | MR15 0 | ||

|

|

| MR16 | 0 | MR17 0 | MR18 | 104 | MR19 | 0 | MR20 0 | ||

|

|

| MR21 | 0 |

|

|

|

|

|

|

|

|

|

|

| Layer 3 Switching Software Feature and Configuration Guide |

|

|

|

|

| ||||

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |||