CY7C0430BV

CY7C0430CV

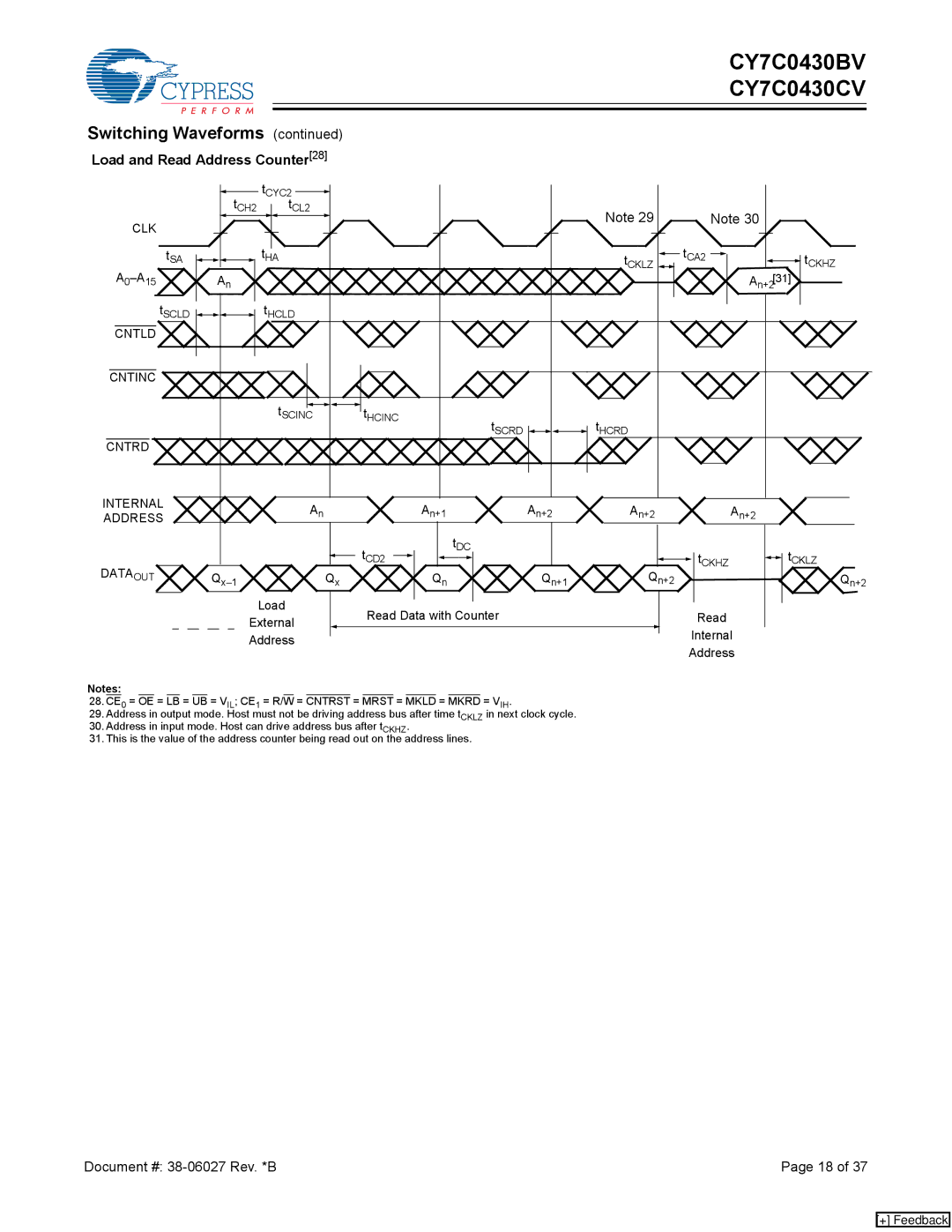

Switching Waveforms (continued)

Load and Read Address Counter[28]

| tCYC2 |

|

|

|

tCH2 | tCL2 | Note 29 |

| Note 30 |

CLK |

|

| ||

|

|

|

| |

tSA | tHA | tCKLZ | tCA2 | tCKHZ |

|

| An |

|

|

|

| An+2[31] | |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

tSCLD ![]()

![]()

![]()

![]() tHCLD

tHCLD

CNTLD

CNTINC ![]()

![]()

![]()

![]()

tSCINC |

|

|

| tHCINC | tSCRD |

|

|

| tHCRD |

|

|

|

|

|

|

|

|

CNTRD

INTERNAL |

|

| An | An+1 | An+2 | A | n+2 | A | n+2 | |

ADDRESS |

|

| ||||||||

|

|

|

|

|

|

|

| |||

|

|

|

| tCD2 | tDC |

|

| tCKHZ |

| tCKLZ |

DATAOUT |

|

|

|

|

|

|

| |||

Q | Q | Q | Q | n+1 |

| Qn+2 |

| Q | ||

|

| x | n |

|

|

|

| n+2 | ||

Load | Read Data with Counter | Read |

External | ||

Address |

| Internal |

| Address | |

|

|

Notes:

28.CE0 = OE = LB = UB = VIL; CE1 = R/W = CNTRST = MRST = MKLD = MKRD = VIH.

29.Address in output mode. Host must not be driving address bus after time tCKLZ in next clock cycle.

30.Address in input mode. Host can drive address bus after tCKHZ.

31.This is the value of the address counter being read out on the address lines.

Document #: | Page 18 of 37 |

[+] Feedback