PRELIMINARY CY8CNP102B, CY8CNP102E

In the following table, tHRECALL starts from the time Vcc rises above VSWITCH. If an SRAM WRITE has not taken place since the last nonvolatile cycle, no STORE takes place. Industrial grade devices require 15 ms maximum.

Table 34. 5V nvSRAM AutoStore/Power Up RECALL (CY8CNP102E)

Parameter |

| Description |

|

|

|

|

| nvSRAM |

| Unit | |||

|

|

|

|

| Min |

|

| Max |

| ||||

|

|

|

|

|

|

|

|

|

|

|

| ||

tHRECALL |

| Power Up RECALL Duration |

|

|

|

|

|

|

| 20 |

| ms | |

tSTORE |

| STORE Cycle Duration |

|

|

|

|

|

|

| 12.5 |

| ms | |

VSWITCH |

| Low Voltage Trigger Level |

|

|

|

|

|

|

| 4.4 |

| V | |

tVccRISE |

| VCC Rise Time |

|

|

|

| 150 |

|

|

|

| μs | |

AC General Purpose IO Specifications |

|

|

|

|

|

|

|

|

|

| |||

Table 35. 5V AC GPIO Specifications (CY8CNP102E) |

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| |||

Symbol |

|

| Description | Min | Typ |

| Max | Units |

| Notes | |||

FGPIO |

| GPIO Operating Frequency | 0 | – |

| 12.3 | MHz | Normal Strong Mode | |||||

TRiseF |

| Rise Time, Normal Strong Mode, Cload = 50 pF | 3 | – |

| 18 | ns | Vcc = 4.75V to 5.25V | |||||

|

|

|

|

|

|

|

|

|

|

| 10% - 90% |

|

|

TFallF |

| Fall Time, Normal Strong Mode, Cload = 50 pF | 2 | – |

| 18 | ns | Vcc = 4.75V to 5.25V | |||||

|

|

|

|

|

|

|

|

|

|

| 10% - 90% |

|

|

|

|

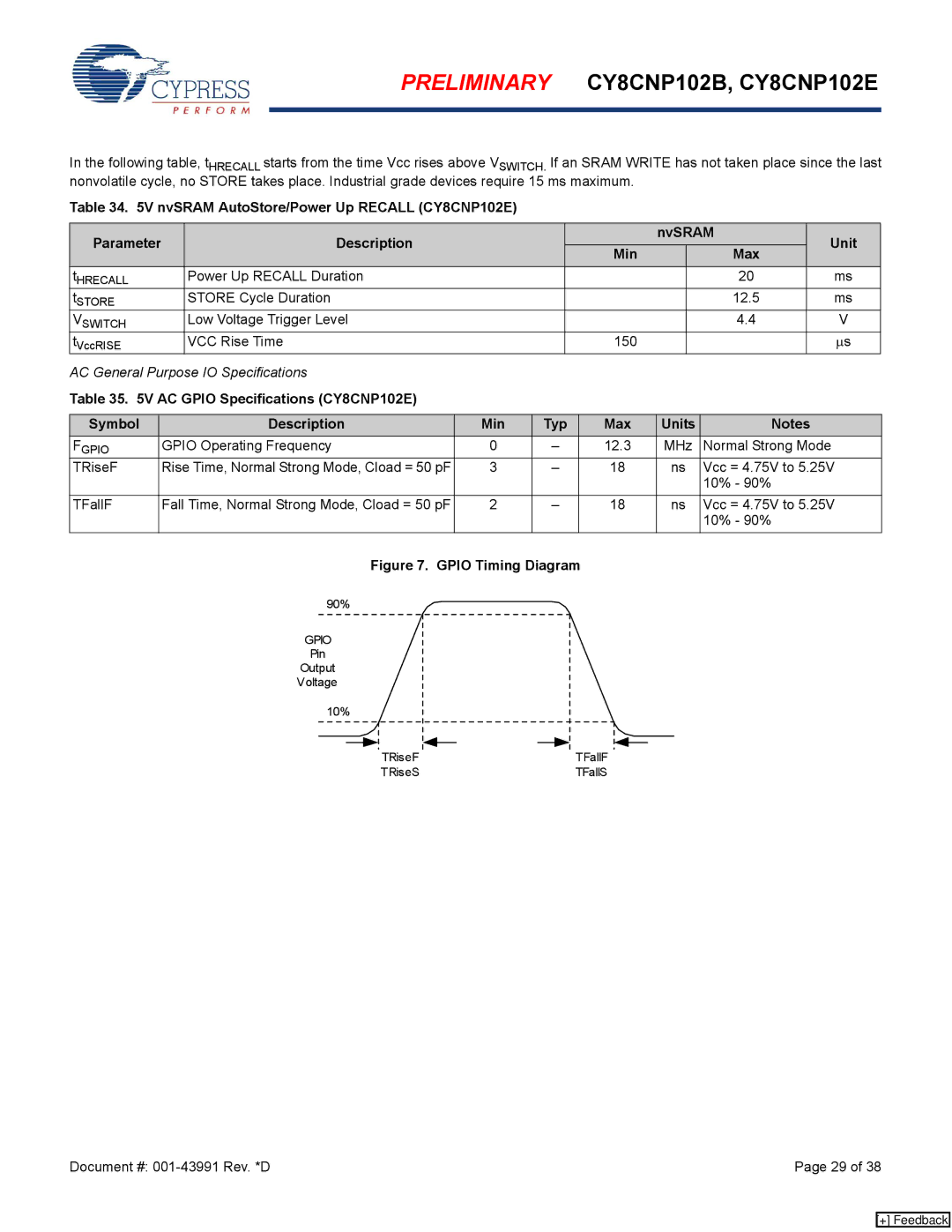

| Figure 7. GPIO Timing Diagram |

|

|

|

|

|

| ||||

90%

GPIO

Pin

Output

Voltage

10%

TRiseF | TFallF |

TRiseS | TFallS |

Document #: | Page 29 of 38 |

[+] Feedback