PRELIMINARY CY8CNP102B, CY8CNP102E

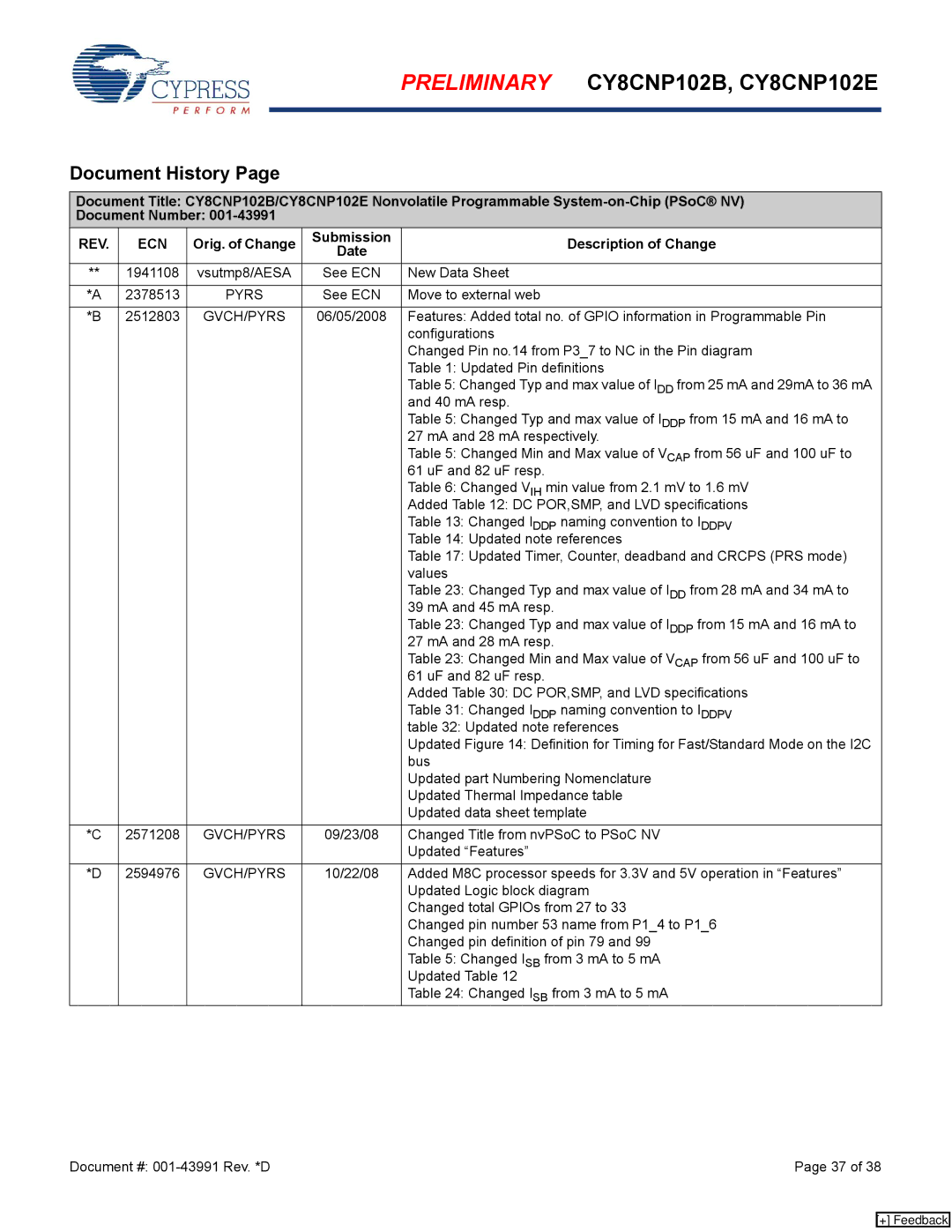

Document History Page

Document Title: CY8CNP102B/CY8CNP102E Nonvolatile Programmable

Document Number:

REV. | ECN | Orig. of Change | Submission | Description of Change | |

Date | |||||

|

|

|

| ||

|

|

|

|

| |

** | 1941108 | vsutmp8/AESA | See ECN | New Data Sheet | |

|

|

|

|

| |

*A | 2378513 | PYRS | See ECN | Move to external web | |

|

|

|

|

| |

*B | 2512803 | GVCH/PYRS | 06/05/2008 | Features: Added total no. of GPIO information in Programmable Pin | |

|

|

|

| configurations | |

|

|

|

| Changed Pin no.14 from P3_7 to NC in the Pin diagram | |

|

|

|

| Table 1: Updated Pin definitions | |

|

|

|

| Table 5: Changed Typ and max value of IDD from 25 mA and 29mA to 36 mA | |

|

|

|

| and 40 mA resp. | |

|

|

|

| Table 5: Changed Typ and max value of IDDP from 15 mA and 16 mA to | |

|

|

|

| 27 mA and 28 mA respectively. | |

|

|

|

| Table 5: Changed Min and Max value of VCAP from 56 uF and 100 uF to | |

|

|

|

| 61 uF and 82 uF resp. | |

|

|

|

| Table 6: Changed VIH min value from 2.1 mV to 1.6 mV | |

|

|

|

| Added Table 12: DC POR,SMP, and LVD specifications | |

|

|

|

| Table 13: Changed IDDP naming convention to IDDPV | |

|

|

|

| Table 14: Updated note references | |

|

|

|

| Table 17: Updated Timer, Counter, deadband and CRCPS (PRS mode) | |

|

|

|

| values | |

|

|

|

| Table 23: Changed Typ and max value of IDD from 28 mA and 34 mA to | |

|

|

|

| 39 mA and 45 mA resp. | |

|

|

|

| Table 23: Changed Typ and max value of IDDP from 15 mA and 16 mA to | |

|

|

|

| 27 mA and 28 mA resp. | |

|

|

|

| Table 23: Changed Min and Max value of VCAP from 56 uF and 100 uF to | |

|

|

|

| 61 uF and 82 uF resp. | |

|

|

|

| Added Table 30: DC POR,SMP, and LVD specifications | |

|

|

|

| Table 31: Changed IDDP naming convention to IDDPV | |

|

|

|

| table 32: Updated note references | |

|

|

|

| Updated Figure 14: Definition for Timing for Fast/Standard Mode on the I2C | |

|

|

|

| bus | |

|

|

|

| Updated part Numbering Nomenclature | |

|

|

|

| Updated Thermal Impedance table | |

|

|

|

| Updated data sheet template | |

|

|

|

|

| |

*C | 2571208 | GVCH/PYRS | 09/23/08 | Changed Title from nvPSoC to PSoC NV | |

|

|

|

| Updated “Features” | |

|

|

|

|

| |

*D | 2594976 | GVCH/PYRS | 10/22/08 | Added M8C processor speeds for 3.3V and 5V operation in “Features” | |

|

|

|

| Updated Logic block diagram | |

|

|

|

| Changed total GPIOs from 27 to 33 | |

|

|

|

| Changed pin number 53 name from P1_4 to P1_6 | |

|

|

|

| Changed pin definition of pin 79 and 99 | |

|

|

|

| Table 5: Changed ISB from 3 mA to 5 mA | |

|

|

|

| Updated Table 12 | |

|

|

|

| Table 24: Changed ISB from 3 mA to 5 mA |

Document #: | Page 37 of 38 |

[+] Feedback