PRELIMINARY CY8CNP102B, CY8CNP102E

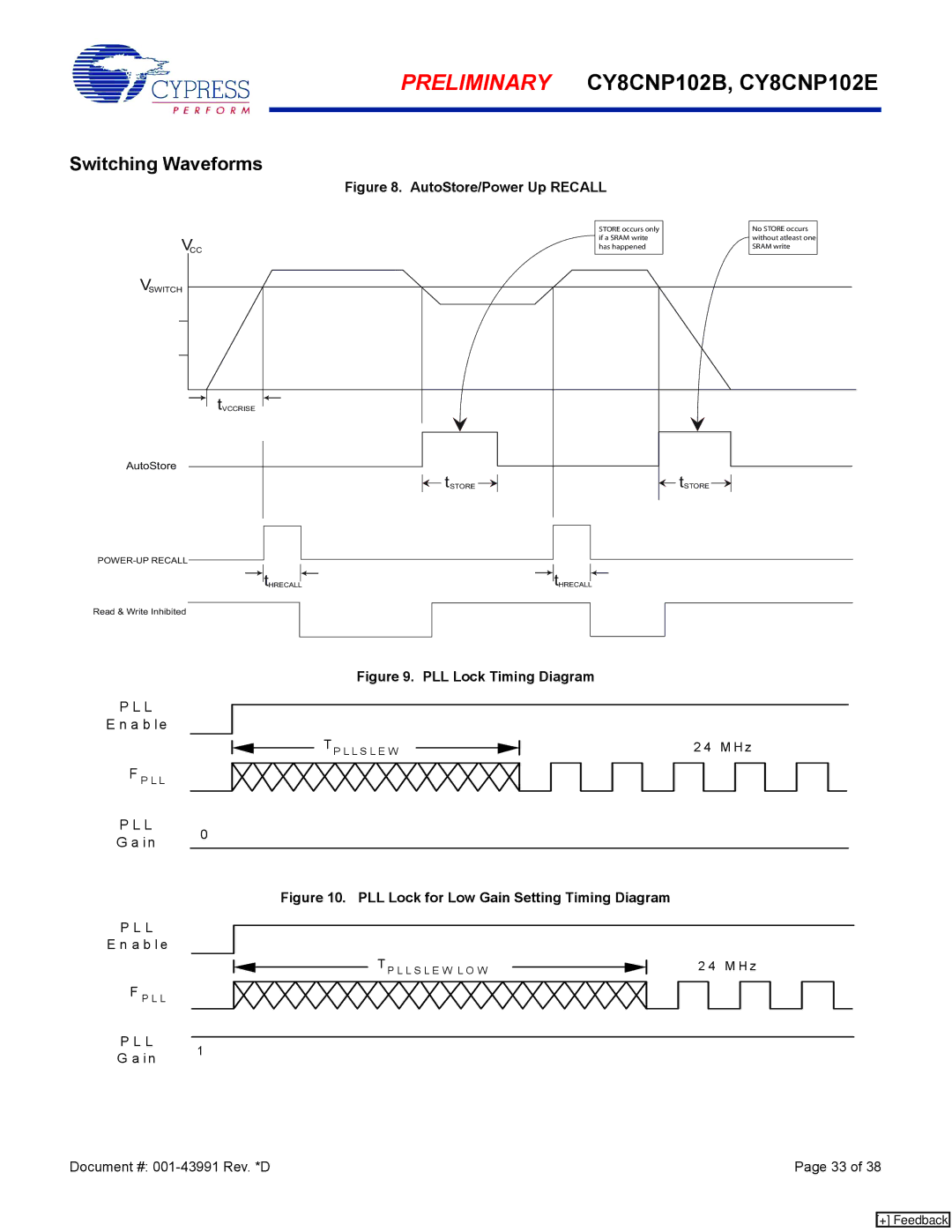

Switching Waveforms

Figure 8. AutoStore/Power Up RECALL

| STORE occurs only | No STORE occurs | |

VCC | if a SRAM write | without atleast one | |

has happened | SRAM write | ||

|

VSWITCH |

|

tVCCRISE |

|

AutoStore | tSTORE |

tSTORE |

tHRECALL

tHRECALL

Read & Write Inhibited

Figure 9. PLL Lock Timing Diagram

P L L

E n a b l e

T P L L S L E W

F P L L

P L L | 0 | |

G a in | ||

|

2 4 M H z

Figure 10. PLL Lock for Low Gain Setting Timing Diagram

P L L

E n a b l e

T P L L S L E W L O W |

|

| 2 4 M H z |

|

| ||

| |||

|

|

F P L L

P L L |

| |

1 | ||

G a i n | ||

|

Document #: | Page 33 of 38 |

[+] Feedback