PRELIMINARY CY8CNP102B, CY8CNP102E

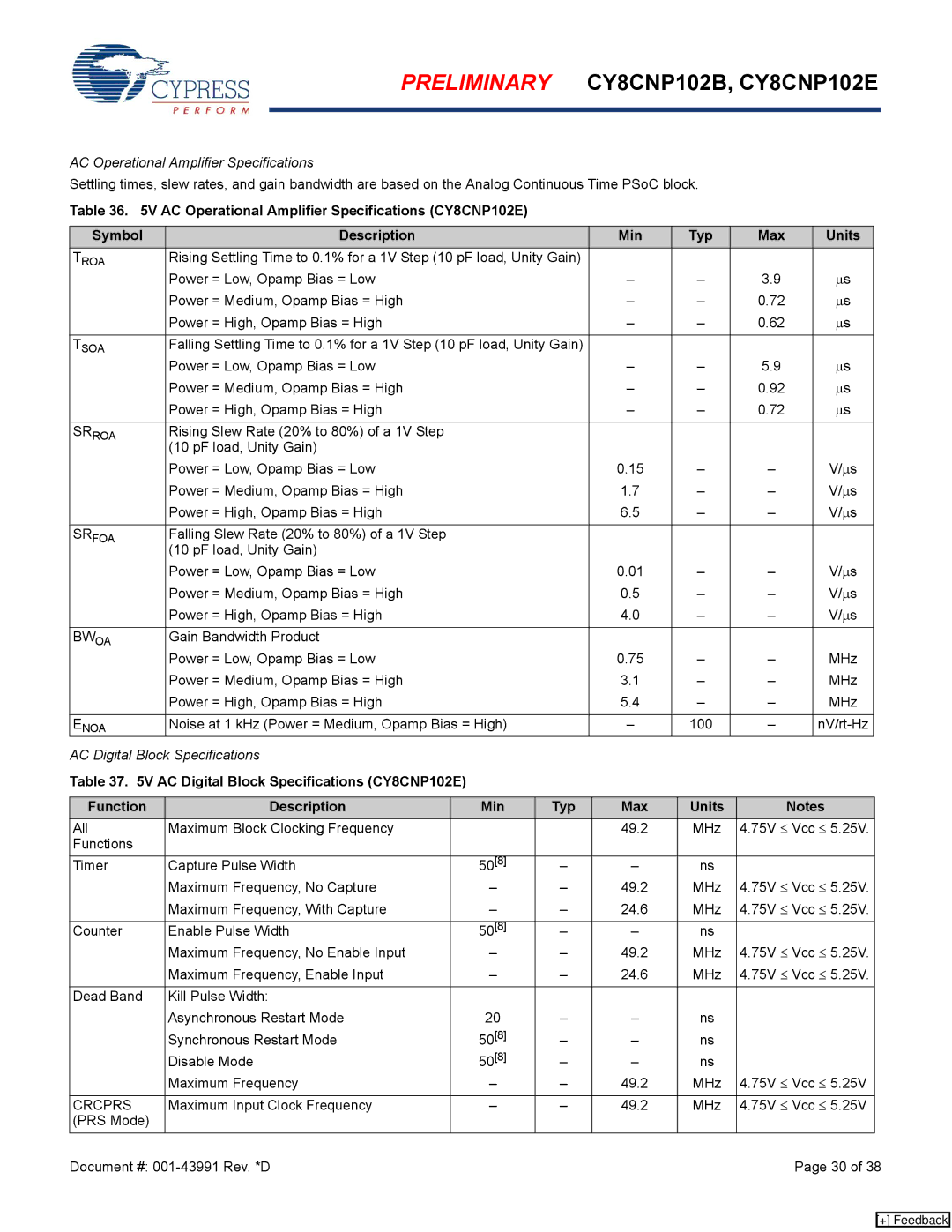

AC Operational Amplifier Specifications

Settling times, slew rates, and gain bandwidth are based on the Analog Continuous Time PSoC block.

Table 36. 5V AC Operational Amplifier Specifications (CY8CNP102E)

Symbol | Description |

|

| Min | Typ |

| Max |

| Units |

| |

TROA | Rising Settling Time to 0.1% for a 1V Step (10 pF load, Unity Gain) |

|

|

|

|

|

|

| |||

| Power = Low, Opamp Bias = Low |

|

| – | – | 3.9 |

| μs |

| ||

| Power = Medium, Opamp Bias = High |

|

| – | – | 0.72 |

| μs |

| ||

| Power = High, Opamp Bias = High |

|

| – | – | 0.62 |

| μs |

| ||

|

|

|

|

|

|

|

|

|

|

| |

TSOA | Falling Settling Time to 0.1% for a 1V Step (10 pF load, Unity Gain) |

|

|

|

|

|

|

| |||

| Power = Low, Opamp Bias = Low |

|

| – | – | 5.9 |

| μs |

| ||

| Power = Medium, Opamp Bias = High |

|

| – | – | 0.92 |

| μs |

| ||

| Power = High, Opamp Bias = High |

|

| – | – | 0.72 |

| μs |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

SRROA | Rising Slew Rate (20% to 80%) of a 1V Step |

|

|

|

|

|

|

|

|

| |

| (10 pF load, Unity Gain) |

|

|

|

|

|

|

|

|

| |

| Power = Low, Opamp Bias = Low |

|

| 0.15 | – |

| – |

| V/μs |

| |

| Power = Medium, Opamp Bias = High |

|

| 1.7 | – |

| – |

| V/μs |

| |

| Power = High, Opamp Bias = High |

|

| 6.5 | – |

| – |

| V/μs |

| |

|

|

|

|

|

|

|

|

|

|

|

|

SRFOA | Falling Slew Rate (20% to 80%) of a 1V Step |

|

|

|

|

|

|

|

|

| |

| (10 pF load, Unity Gain) |

|

|

|

|

|

|

|

|

| |

| Power = Low, Opamp Bias = Low |

|

| 0.01 | – |

| – |

| V/μs |

| |

| Power = Medium, Opamp Bias = High |

|

| 0.5 | – |

| – |

| V/μs |

| |

| Power = High, Opamp Bias = High |

|

| 4.0 | – |

| – |

| V/μs |

| |

|

|

|

|

|

|

|

|

|

|

|

|

BWOA | Gain Bandwidth Product |

|

|

|

|

|

|

|

|

| |

| Power = Low, Opamp Bias = Low |

|

| 0.75 | – |

| – |

| MHz |

| |

| Power = Medium, Opamp Bias = High |

|

| 3.1 | – |

| – |

| MHz |

| |

| Power = High, Opamp Bias = High |

|

| 5.4 | – |

| – |

| MHz |

| |

|

|

|

|

|

|

|

|

|

|

| |

ENOA | Noise at 1 kHz (Power = Medium, Opamp Bias = High) |

| – | 100 |

| – |

|

| |||

AC Digital Block Specifications |

|

|

|

|

|

|

|

|

| ||

Table 37. 5V AC Digital Block Specifications (CY8CNP102E) |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

Function | Description |

| Min | Typ | Max | Units |

|

| Notes |

| |

All | Maximum Block Clocking Frequency |

|

|

| 49.2 | MHz |

| 4.75V ≤ Vcc ≤ 5.25V. |

| ||

Functions |

|

|

|

|

|

|

|

|

|

|

|

Timer | Capture Pulse Width |

| 50[8] | – | – | ns |

|

|

|

|

|

| Maximum Frequency, No Capture |

| – | – | 49.2 | MHz |

| 4.75V ≤ Vcc ≤ 5.25V. |

| ||

| Maximum Frequency, With Capture |

| – | – | 24.6 | MHz |

| 4.75V ≤ Vcc ≤ 5.25V. |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

Counter | Enable Pulse Width |

| 50[8] | – | – | ns |

|

|

|

|

|

| Maximum Frequency, No Enable Input |

| – | – | 49.2 | MHz |

| 4.75V ≤ Vcc ≤ 5.25V. |

| ||

| Maximum Frequency, Enable Input |

| – | – | 24.6 | MHz |

| 4.75V ≤ Vcc ≤ 5.25V. |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

Dead Band | Kill Pulse Width: |

|

|

|

|

|

|

|

|

|

|

| Asynchronous Restart Mode |

| 20 | – | – | ns |

|

|

|

|

|

| Synchronous Restart Mode |

| 50[8] | – | – | ns |

|

|

|

|

|

| Disable Mode |

| 50[8] | – | – | ns |

|

|

|

|

|

| Maximum Frequency |

| – | – | 49.2 | MHz |

| 4.75V ≤ Vcc ≤ 5.25V |

| ||

|

|

|

|

|

|

|

|

|

| ||

CRCPRS | Maximum Input Clock Frequency |

| – | – | 49.2 | MHz |

| 4.75V ≤ Vcc ≤ 5.25V |

| ||

(PRS Mode) |

|

|

|

|

|

|

|

|

|

|

|

Document #: |

|

|

|

|

|

| Page 30 of 38 | ||||

[+] Feedback