SL811HS

SL811HS Embedded USB Host/Slave Controller

Features

•First USB Host/Slave controller for embedded systems in the market with a standard microprocessor bus interface

•Supports both full speed (12 Mbps) and low speed (1.5 Mbps) USB transfer in both master and slave modes

•Conforms to USB Specification 1.1 for full- and low speed

•Operates as a single USB host or slave under software control

•Automatic detection of either low- or full speed devices

•

•

•

•

•

•Operates from 12 or 48 MHz crystal or oscillator

•

•Suspend/resume, wake up, and

•

•

•Development kit including source code drivers is available

•3.3V power source, 0.35 micron CMOS technology

•Available in both a

Introduction

The SL811HS is an Embedded USB Host/Slave Controller capable of communicating in either full speed or low speed. The SL811HS interfaces to devices such as microprocessors, microcontrollers, DSPs, or directly to a variety of buses such as ISA, PCMCIA, and others. The SL811HS USB Host Controller conforms to USB Specification 1.1.

The SL811HS incorporates USB Serial Interface functionality along with internal full or low speed transceivers. The SL811HS supports and operates in USB full speed mode at 12 Mbps, or in low speed mode at 1.5 Mbps. When in host mode, the SL811HS is the master and controls the USB bus and the devices that are connected to it. In peripheral mode, otherwise known as a slave device, the SL811HS operates as a variety of full- or low speed devices.

The SL811HS data port and microprocessor interface provide an

The available package types offered are a

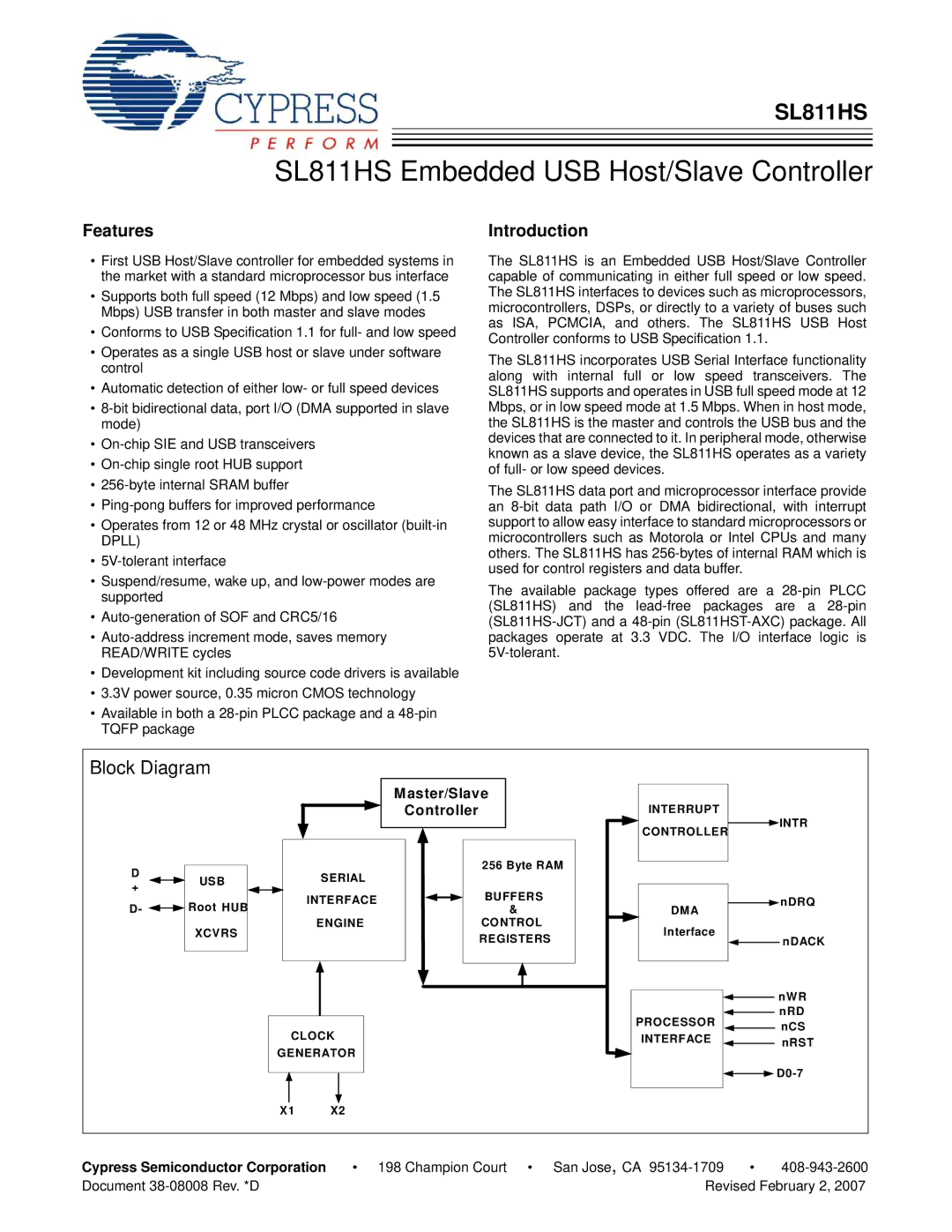

Block Diagram |

|

|

|

|

|

|

| |

|

|

|

| Master/Slave |

|

|

|

|

|

|

|

| Controller |

| INTERRUPT |

| INTR |

|

|

|

|

|

| CONTROLLER |

| |

|

|

|

|

|

|

|

| |

D |

| SERIAL | 256 Byte RAM |

|

| |||

USB |

|

|

|

|

| |||

+ | BUFFERS |

|

|

| ||||

| INTERFACE |

|

| nDRQ | ||||

D- | Root HUB | DMA |

| |||||

|

|

| & |

|

| |||

| XCVRS | ENGINE | CONTROL | Interface |

|

| ||

|

|

| REGISTERS |

| nDACK | |||

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| nWR |

|

|

|

|

|

| PROCESSOR |

| nRD |

| CLOCK |

|

|

|

| nCS | ||

|

|

|

| INTERFACE |

| |||

|

|

|

|

| nRST | |||

| GENERATOR |

|

|

|

|

| ||

|

|

|

|

|

|

|

| |

| X1 | X2 |

|

|

|

|

|

|

Cypress Semiconductor Corporation | • | 198 Champion Court | • | San Jose, CA | • | |||

Document |

|

|

|

| Revised February 2, 2007 | |||