|

|

|

|

|

|

|

|

|

|

|

|

|

| SL811HS | |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

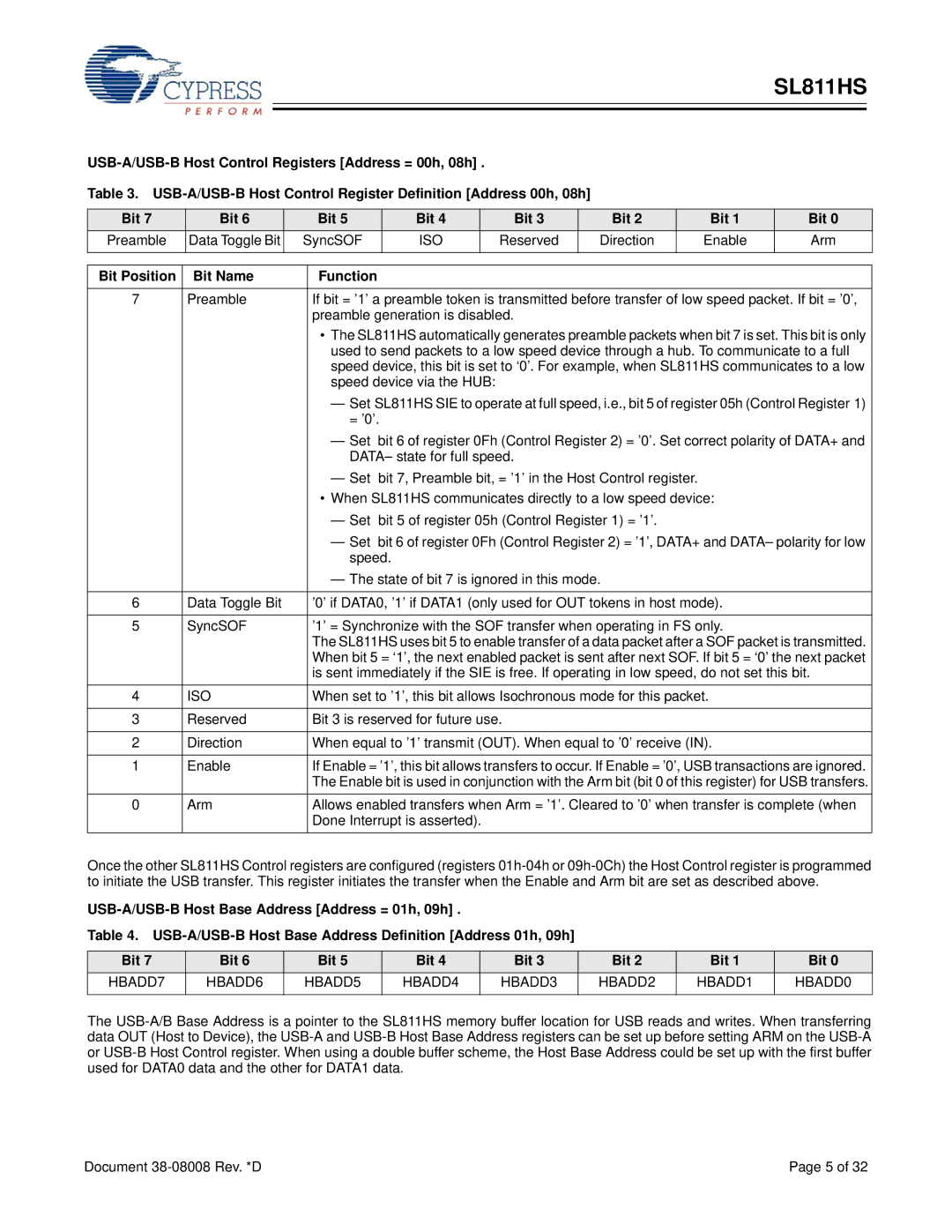

Table 3. |

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Bit 7 | Bit 6 |

| Bit 5 | Bit 4 |

| Bit 3 |

| Bit 2 |

| Bit 1 | Bit 0 | ||||

Preamble | Data Toggle Bit | SyncSOF | ISO |

| Reserved |

| Direction |

| Enable | Arm | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Bit Position |

| Bit Name |

| Function |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| |||||||||||

7 |

| Preamble |

| If bit = ’1’ a preamble token is transmitted before transfer of low speed packet. If bit = ’0’, | |||||||||||

|

|

|

|

|

| preamble generation is disabled. |

|

|

|

|

| ||||

|

|

|

|

|

| • The SL811HS automatically generates preamble packets when bit 7 is set. This bit is only | |||||||||

|

|

|

|

|

| used to send packets to a low speed device through a hub. To communicate to a full | |||||||||

|

|

|

|

|

| speed device, this bit is set to ‘0’. For example, when SL811HS communicates to a low | |||||||||

|

|

|

|

|

| speed device via the HUB: |

|

|

|

|

|

|

| ||

|

|

|

|

|

| — Set SL811HS SIE to operate at full speed, i.e., bit 5 of register 05h (Control Register 1) | |||||||||

|

|

|

|

|

| = ’0’. |

|

|

|

|

|

|

| ||

|

|

|

|

|

| — Set | bit 6 of register 0Fh (Control Register 2) = ’0’. Set correct polarity of DATA+ and | ||||||||

|

|

|

|

|

| DATA– state for full speed. |

|

|

|

|

| ||||

|

|

|

|

|

| — Set | bit 7, Preamble bit, = ’1’ in the Host Control register. |

|

|

| |||||

|

|

|

|

|

| • When SL811HS communicates directly to a low speed device: |

|

| |||||||

|

|

|

|

|

| — Set | bit 5 of register 05h (Control Register 1) = ’1’. |

|

|

| |||||

|

|

|

|

|

| — Set bit 6 of register 0Fh (Control Register 2) = ’1’, DATA+ and DATA– polarity for low | |||||||||

|

|

|

|

|

| speed. |

|

|

|

|

|

|

| ||

|

|

|

|

|

| — The state of bit 7 is ignored in this mode. |

|

|

| ||||||

|

|

|

|

|

|

| |||||||||

6 |

| Data Toggle Bit |

| ’0’ if DATA0, ’1’ if DATA1 (only used for OUT tokens in host mode). |

|

| |||||||||

|

|

|

|

|

|

| |||||||||

5 |

| SyncSOF |

| ’1’ = Synchronize with the SOF transfer when operating in FS only. |

|

| |||||||||

|

|

|

|

|

| The SL811HS uses bit 5 to enable transfer of a data packet after a SOF packet is transmitted. | |||||||||

|

|

|

|

|

| When bit 5 = ‘1’, the next enabled packet is sent after next SOF. If bit 5 = ‘0’ the next packet | |||||||||

|

|

|

|

|

| is sent immediately if the SIE is free. If operating in low speed, do not set this bit. | |||||||||

4 |

| ISO |

| When set to ’1’, this bit allows Isochronous mode for this packet. |

|

| |||||||||

|

|

|

|

|

|

|

|

|

| ||||||

3 |

| Reserved |

| Bit 3 is reserved for future use. |

|

|

|

|

| ||||||

|

|

|

|

|

|

| |||||||||

2 |

| Direction |

| When equal to ’1’ transmit (OUT). When equal to ’0’ receive (IN). |

|

| |||||||||

|

|

|

|

| |||||||||||

1 |

| Enable |

| If Enable = ’1’, this bit allows transfers to occur. If Enable = ’0’, USB transactions are ignored. | |||||||||||

|

|

|

|

|

| The Enable bit is used in conjunction with the Arm bit (bit 0 of this register) for USB transfers. | |||||||||

0 |

| Arm |

| Allows enabled transfers when Arm = ’1’. Cleared to ’0’ when transfer is complete (when | |||||||||||

|

|

|

|

|

| Done Interrupt is asserted). |

|

|

|

|

|

|

| ||

Once the other SL811HS Control registers are configured (registers

Table 4.

Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

HBADD7 | HBADD6 | HBADD5 | HBADD4 | HBADD3 | HBADD2 | HBADD1 | HBADD0 |

|

|

|

|

|

|

|

|

The

Document | Page 5 of 32 |