SL811HS

Endpoint Control Registers

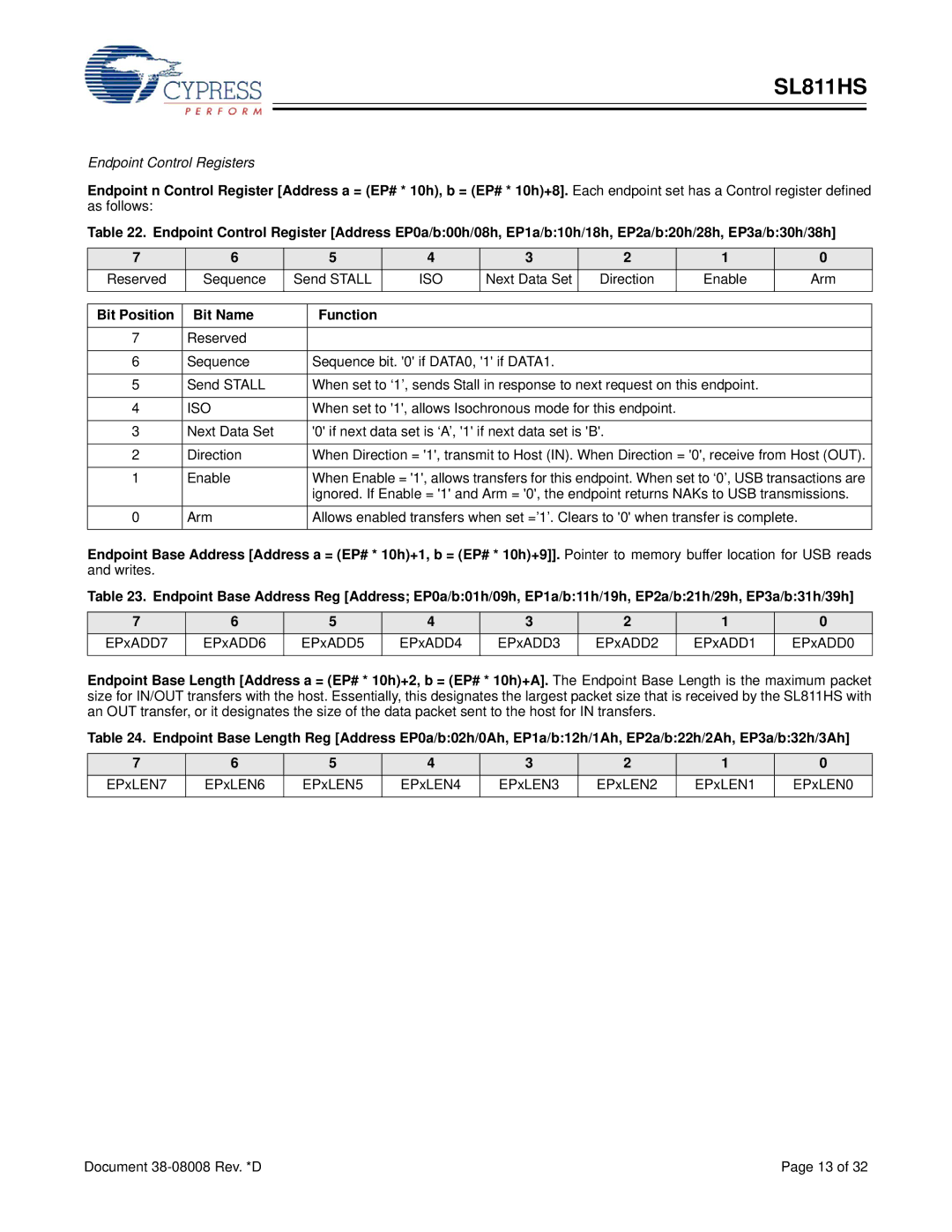

Endpoint n Control Register [Address a = (EP# * 10h), b = (EP# * 10h)+8]. Each endpoint set has a Control register defined as follows:

Table 22. Endpoint Control Register [Address EP0a/b:00h/08h, EP1a/b:10h/18h, EP2a/b:20h/28h, EP3a/b:30h/38h]

7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 | |

Reserved | Sequence | Send STALL | ISO | Next Data Set | Direction | Enable |

| Arm | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit Position | Bit Name |

| Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 | Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

6 | Sequence |

| Sequence bit. '0' if DATA0, '1' if DATA1. |

|

|

|

| ||

|

|

|

|

| |||||

5 | Send STALL |

| When set to ‘1’, sends Stall in response to next request on this endpoint. |

| |||||

|

|

|

|

|

|

| |||

4 | ISO |

| When set to '1', allows Isochronous mode for this endpoint. |

|

|

| |||

|

|

|

|

|

|

| |||

3 | Next Data Set |

| '0' if next data set is ‘A’, '1' if next data set is 'B'. |

|

|

| |||

|

|

|

| ||||||

2 | Direction |

| When Direction = '1', transmit to Host (IN). When Direction = '0', receive from Host (OUT). | ||||||

|

|

|

| ||||||

1 | Enable |

| When Enable = '1', allows transfers for this endpoint. When set to ‘0’, USB transactions are | ||||||

|

|

| ignored. If Enable = '1' and Arm = '0', the endpoint returns NAKs to USB transmissions. | ||||||

0 | Arm |

| Allows enabled transfers when set =’1’. Clears to '0' when transfer is complete. |

| |||||

|

|

|

|

|

|

|

|

|

|

Endpoint Base Address [Address a = (EP# * 10h)+1, b = (EP# * 10h)+9]]. Pointer to memory buffer location for USB reads and writes.

Table 23. Endpoint Base Address Reg [Address; EP0a/b:01h/09h, EP1a/b:11h/19h, EP2a/b:21h/29h, EP3a/b:31h/39h]

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

EPxADD7 | EPxADD6 | EPxADD5 | EPxADD4 | EPxADD3 | EPxADD2 | EPxADD1 | EPxADD0 |

|

|

|

|

|

|

|

|

Endpoint Base Length [Address a = (EP# * 10h)+2, b = (EP# * 10h)+A]. The Endpoint Base Length is the maximum packet size for IN/OUT transfers with the host. Essentially, this designates the largest packet size that is received by the SL811HS with an OUT transfer, or it designates the size of the data packet sent to the host for IN transfers.

Table 24. Endpoint Base Length Reg [Address EP0a/b:02h/0Ah, EP1a/b:12h/1Ah, EP2a/b:22h/2Ah, EP3a/b:32h/3Ah]

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

EPxLEN7 | EPxLEN6 | EPxLEN5 | EPxLEN4 | EPxLEN3 | EPxLEN2 | EPxLEN1 | EPxLEN0 |

|

|

|

|

|

|

|

|

Document | Page 13 of 32 |