SL811HS

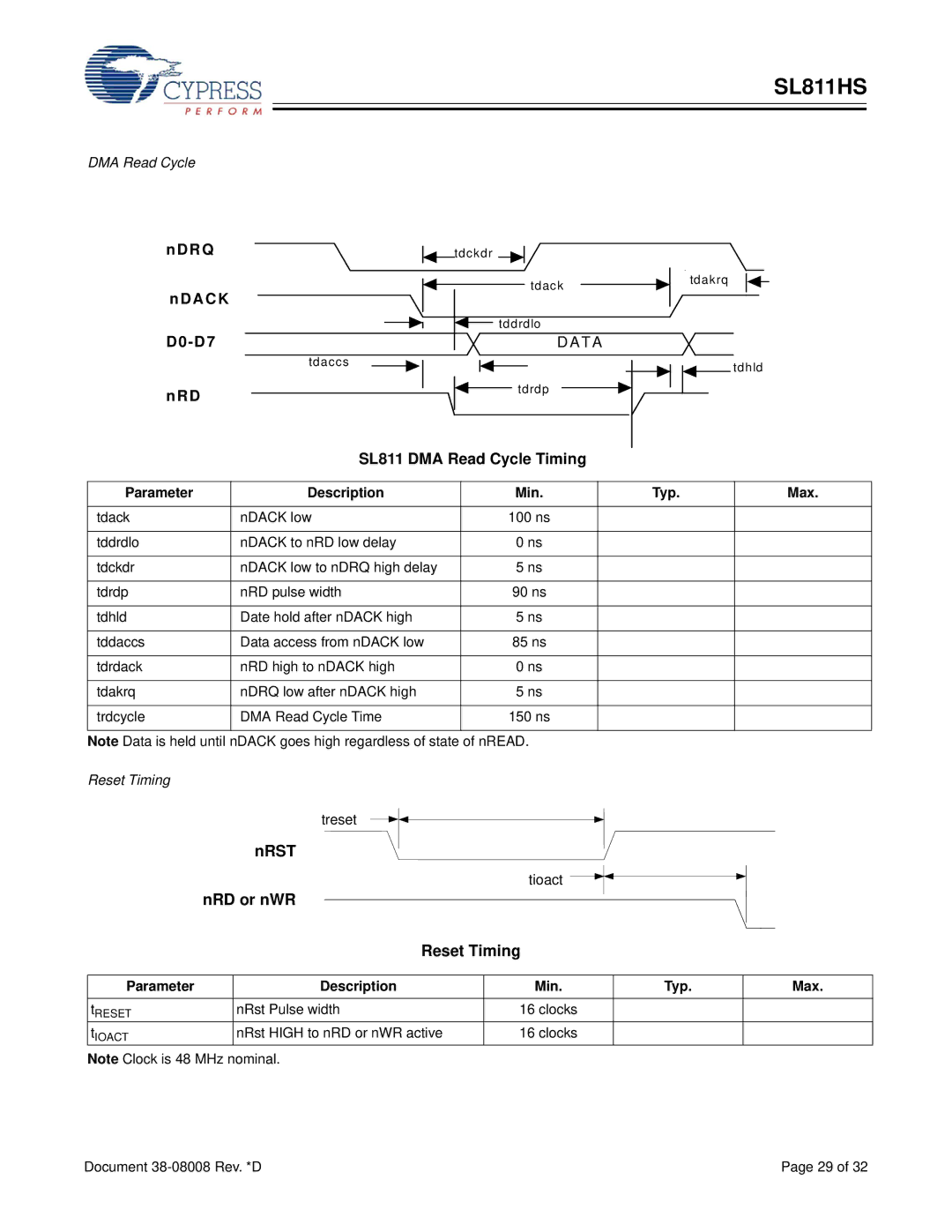

DMA Read Cycle

nDRQ |

|

|

|

|

|

|

|

|

| tdckdr |

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

nDACK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tdack |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tddrdlo |

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DATA |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tdaccs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

nRD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tdrdp |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SL811 DMA Read Cycle Timing

SL811 DMA READ CYCLE TIMING

tdakrq

tdhld

Parameter | Description | Min. | Typ. | Max. |

|

|

|

|

|

tdack | nDACK low | 100 ns |

|

|

|

|

|

|

|

tddrdlo | nDACK to nRD low delay | 0 ns |

|

|

|

|

|

|

|

tdckdr | nDACK low to nDRQ high delay | 5 ns |

|

|

|

|

|

|

|

tdrdp | nRD pulse width | 90 ns |

|

|

|

|

|

|

|

tdhld | Date hold after nDACK high | 5 ns |

|

|

|

|

|

|

|

tddaccs | Data access from nDACK low | 85 ns |

|

|

|

|

|

|

|

tdrdack | nRD high to nDACK high | 0 ns |

|

|

|

|

|

|

|

tdakrq | nDRQ low after nDACK high | 5 ns |

|

|

|

|

|

|

|

trdcycle | DMA Read Cycle Time | 150 ns |

|

|

|

|

|

|

|

Note Data is held until nDACK goes high regardless of state of nREAD.

Reset Timing

treset

nRST

tioact ![]()

![]()

nRD or nWR

Reset Timing

Parameter | Description | Min. | Typ. | Max. |

tRESET | nRst Pulse width | 16 clocks |

|

|

tIOACT | nRst HIGH to nRD or nWR active | 16 clocks |

|

|

Note Clock is 48 MHz nominal.

Document | Page 29 of 32 |