Host Interface

4.3.1.9 ATA Features register

This register is used for the SET FEATURES command.

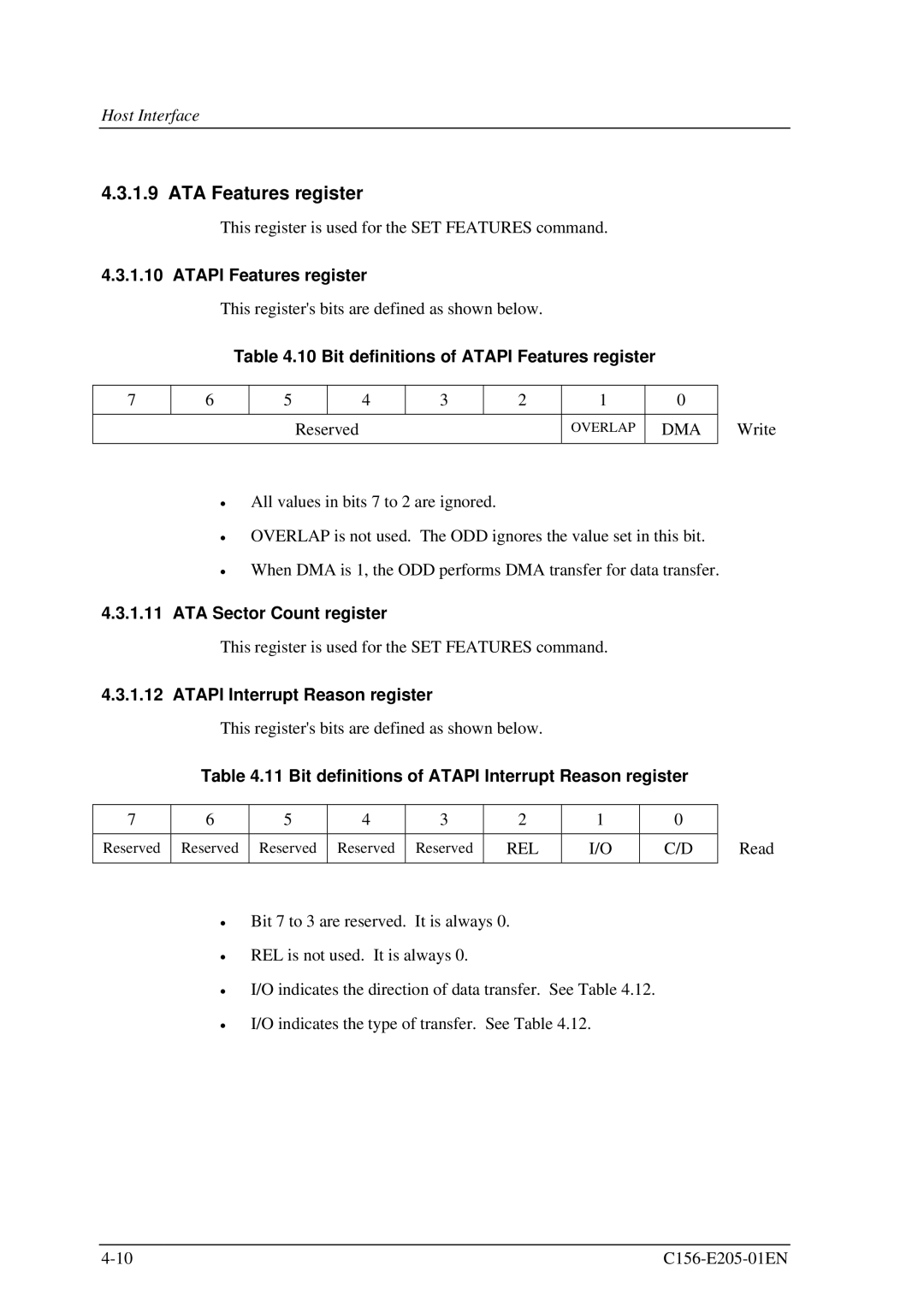

4.3.1.10 ATAPI Features register

This register's bits are defined as shown below.

Table 4.10 Bit definitions of ATAPI Features register

7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

| Reserved |

|

| OVERLAP | DMA | |

|

|

|

|

|

|

|

|

|

Write

!

!

!

All values in bits 7 to 2 are ignored.

OVERLAP is not used. The ODD ignores the value set in this bit. When DMA is 1, the ODD performs DMA transfer for data transfer.

4.3.1.11 ATA Sector Count register

This register is used for the SET FEATURES command.

4.3.1.12 ATAPI Interrupt Reason register

This register's bits are defined as shown below.

| Table 4.11 Bit definitions of ATAPI Interrupt Reason register |

| ||||||

|

|

|

|

|

|

|

|

|

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

Reserved | Reserved | Reserved | Reserved | Reserved | REL | I/O | C/D | Read |

|

|

|

|

|

|

|

|

|

!

!

!

!

Bit 7 to 3 are reserved. It is always 0.

REL is not used. It is always 0.

I/O indicates the direction of data transfer. See Table 4.12. I/O indicates the type of transfer. See Table 4.12.