Interface

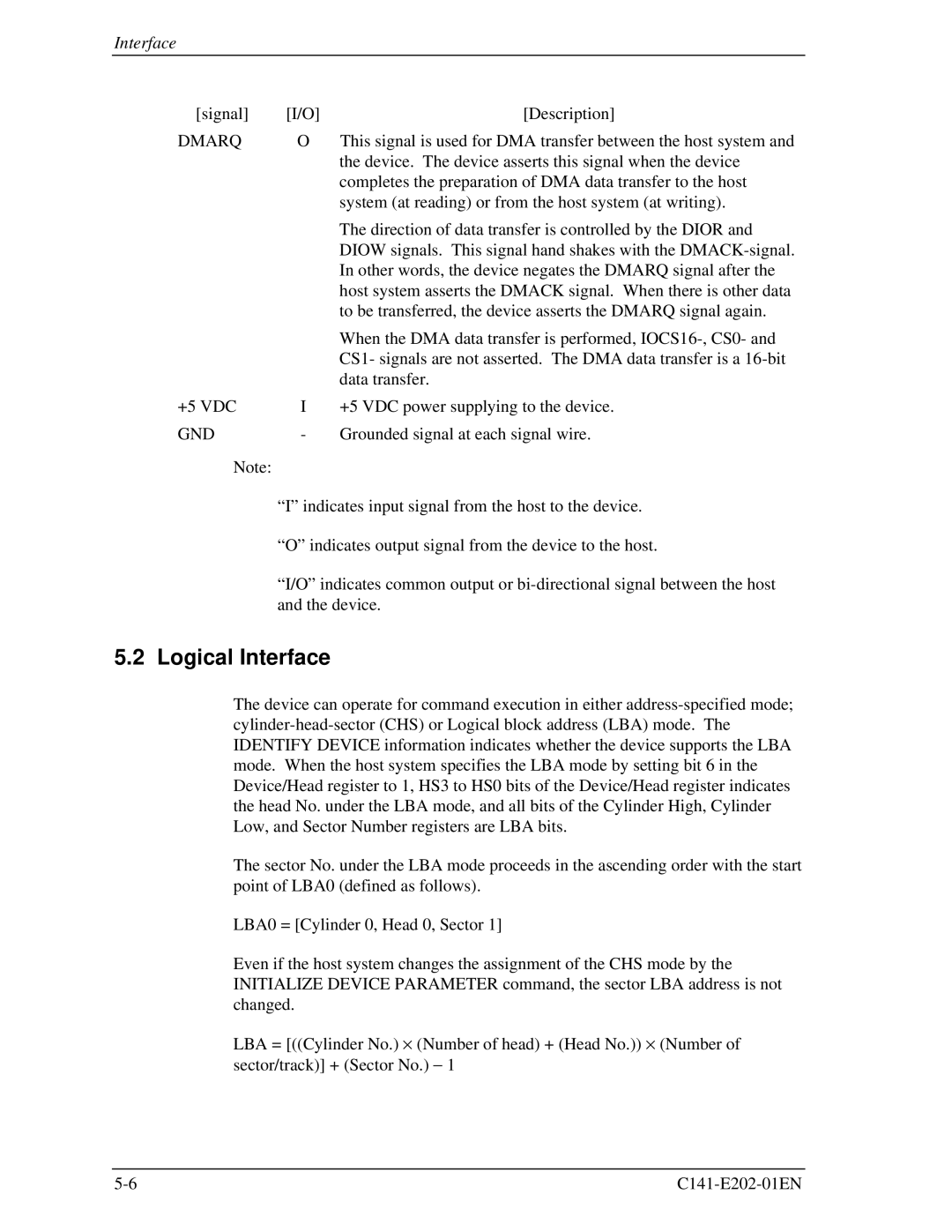

[signal] | [I/O] | [Description] |

DMARQ | O | This signal is used for DMA transfer between the host system and |

|

| the device. The device asserts this signal when the device |

|

| completes the preparation of DMA data transfer to the host |

|

| system (at reading) or from the host system (at writing). |

|

| The direction of data transfer is controlled by the DIOR and |

|

| DIOW signals. This signal hand shakes with the |

|

| In other words, the device negates the DMARQ signal after the |

|

| host system asserts the DMACK signal. When there is other data |

|

| to be transferred, the device asserts the DMARQ signal again. |

|

| When the DMA data transfer is performed, |

|

| CS1- signals are not asserted. The DMA data transfer is a |

|

| data transfer. |

+5 VDC | I | +5 VDC power supplying to the device. |

GND | - | Grounded signal at each signal wire. |

Note: |

|

|

“I” indicates input signal from the host to the device.

“O” indicates output signal from the device to the host.

“I/O” indicates common output or

5.2 Logical Interface

The device can operate for command execution in either

The sector No. under the LBA mode proceeds in the ascending order with the start point of LBA0 (defined as follows).

LBA0 = [Cylinder 0, Head 0, Sector 1]

Even if the host system changes the assignment of the CHS mode by the INITIALIZE DEVICE PARAMETER command, the sector LBA address is not changed.

LBA = [((Cylinder No.) ⋅ (Number of head) + (Head No.)) ⋅ (Number of sector/track)] + (Sector No.) − 1