5.3 Host Commands

(12) STANDBY IMMEDIATE (X’94’ or X’E0’)

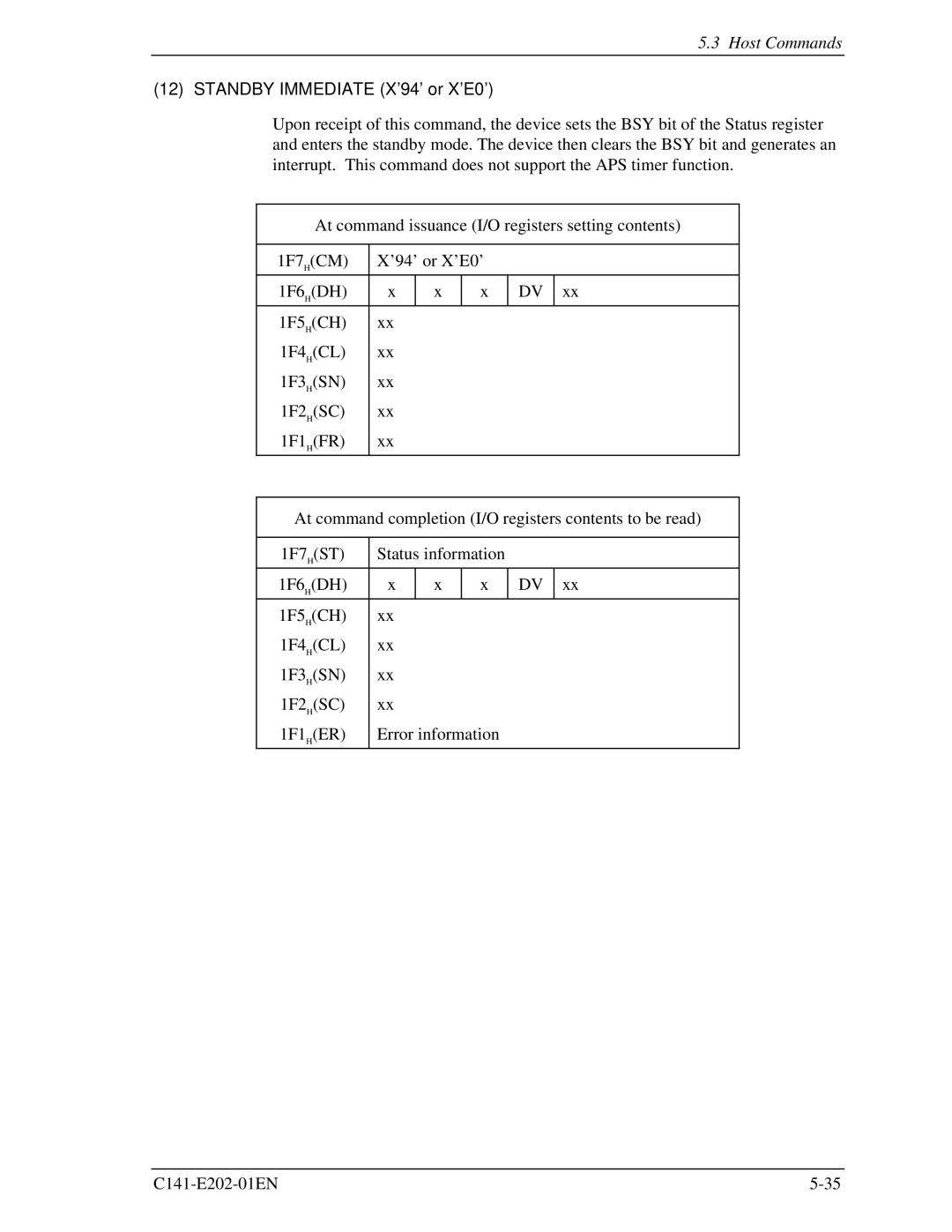

Upon receipt of this command, the device sets the BSY bit of the Status register and enters the standby mode. The device then clears the BSY bit and generates an interrupt. This command does not support the APS timer function.

At command issuance (I/O registers setting contents)

1F7H(CM) | X’94’ or X’E0’ |

|

| ||

1F6H(DH) | x | x | x | DV | xx |

|

|

|

|

|

|

1F5H(CH) | xx |

|

|

|

|

1F4H(CL) | xx |

|

|

|

|

1F3H(SN) | xx |

|

|

|

|

1F2H(SC) | xx |

|

|

|

|

1F1H(FR) | xx |

|

|

|

|

|

|

|

|

|

|

At command completion (I/O registers contents to be read)

1F7H(ST) | Status information |

|

| ||

1F6H(DH) | x | x | x | DV | xx |

|

|

|

|

|

|

1F5H(CH) | xx |

|

|

|

|

1F4H(CL) | xx |

|

|

|

|

1F3H(SN) | xx |

|

|

|

|

1F2H(SC) | xx |

|

|

|

|

1F1H(ER) | Error information |

|

| ||

|

|

|

|

|

|