EM78P312N

8-Bit Microcontroller

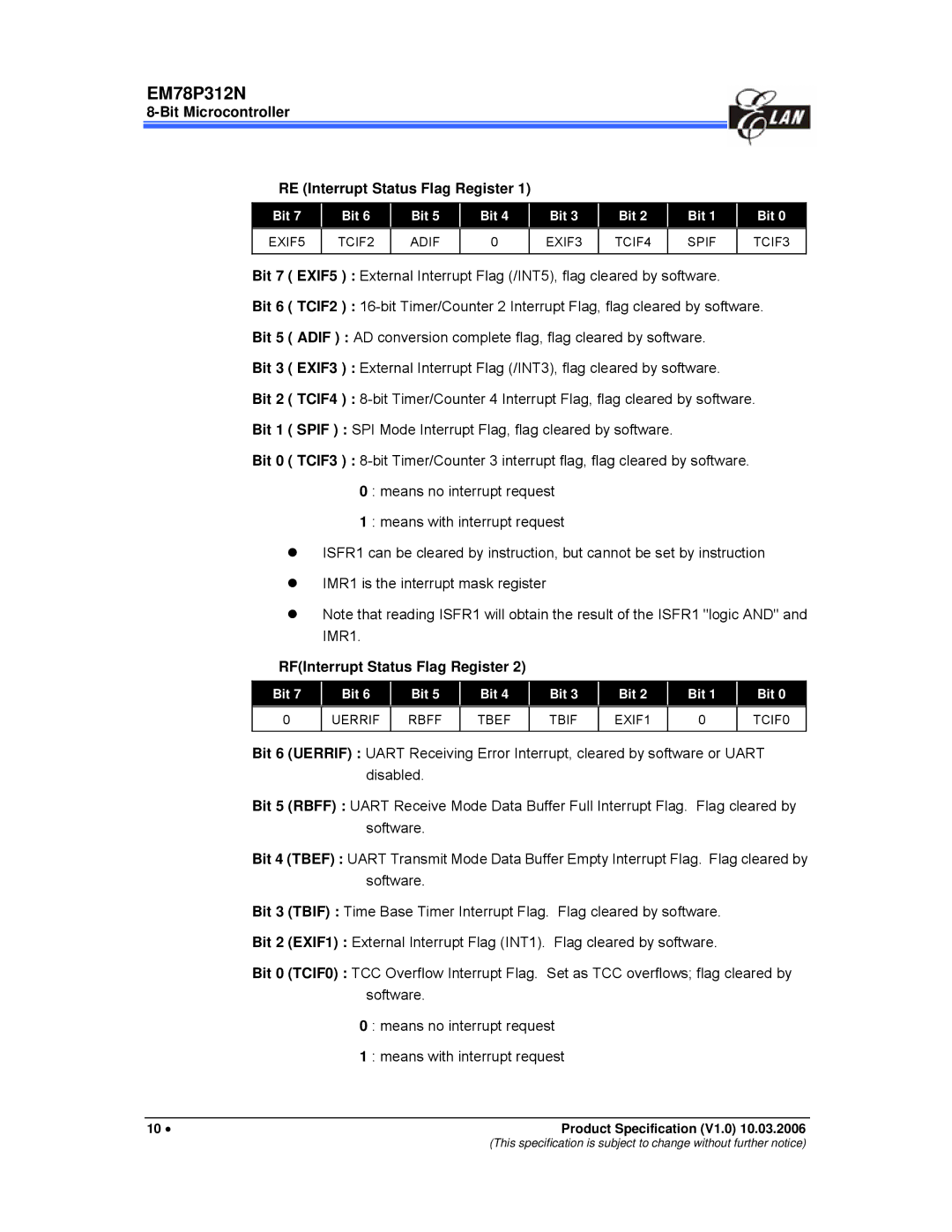

RE (Interrupt Status Flag Register 1)

Bit 7 | Bit 6 | Bit 5 | Bit 4 |

|

|

|

|

Bit 3

Bit 2 | Bit 1 | Bit 0 |

|

|

|

EXIF5

TCIF2

ADIF

0

EXIF3

TCIF4

SPIF

TCIF3

Bit 7 ( EXIF5 ) : External Interrupt Flag (/INT5), flag cleared by software.

Bit 6 ( TCIF2 ) :

Bit 5 ( ADIF ) : AD conversion complete flag, flag cleared by software.

Bit 3 ( EXIF3 ) : External Interrupt Flag (/INT3), flag cleared by software.

Bit 2 ( TCIF4 ) :

Bit 1 ( SPIF ) : SPI Mode Interrupt Flag, flag cleared by software.

Bit 0 ( TCIF3 ) :

1 : means with interrupt request

zISFR1 can be cleared by instruction, but cannot be set by instruction

zIMR1 is the interrupt mask register

zNote that reading ISFR1 will obtain the result of the ISFR1 "logic AND" and IMR1.

RF(Interrupt Status Flag Register 2)

Bit 7 | Bit 6 | Bit 5 | Bit 4 | |

|

|

|

|

Bit 3

Bit 2 | Bit 1 | Bit 0 | |

0

UERRIF

RBFF

TBEF

TBIF

EXIF1

0

TCIF0

Bit 6 (UERRIF) : UART Receiving Error Interrupt, cleared by software or UART disabled.

Bit 5 (RBFF) : UART Receive Mode Data Buffer Full Interrupt Flag. Flag cleared by software.

Bit 4 (TBEF) : UART Transmit Mode Data Buffer Empty Interrupt Flag. Flag cleared by software.

Bit 3 (TBIF) : Time Base Timer Interrupt Flag. Flag cleared by software.

Bit 2 (EXIF1) : External Interrupt Flag (INT1). Flag cleared by software.

Bit 0 (TCIF0) : TCC Overflow Interrupt Flag. Set as TCC overflows; flag cleared by software.

0 : means no interrupt request

1 : means with interrupt request

10 • | Product Specification (V1.0) 10.03.2006 |

(This specification is subject to change without further notice)